Other Parts Discussed in Thread: MSP430G2553, TCA9509

Tool/software: Code Composer Studio

Hello,

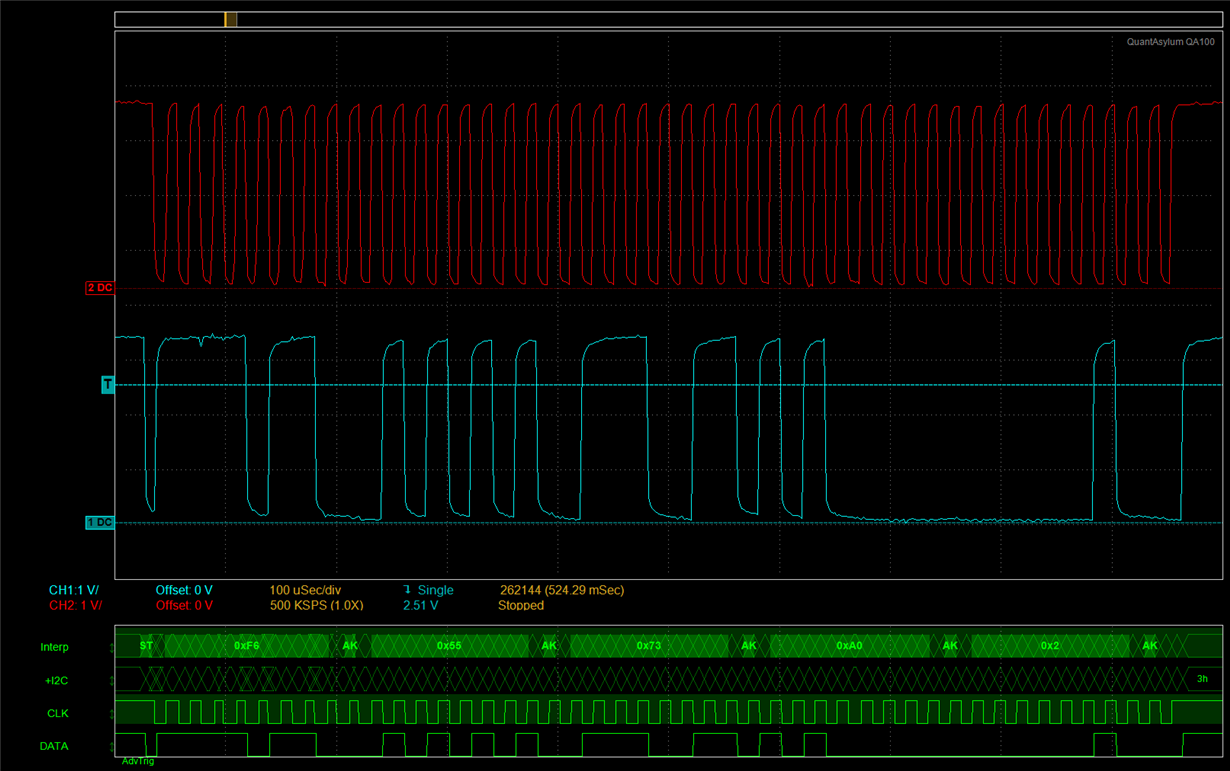

I'm working on a project that can have up to 9 masters all trying to send information to 1 slave. It is a daisy chain connection. 1 is the slave, and then 2-10 are the masters. I have been able to get 3 and 4 masters consistently transmitting data correctly, but once I add 5, 6, and 7 masters things start to get inconsistent. I'm using buffer chip, TCA9509DGKR, to account for the capacitance in the system. In the Errata sheet of the MSP430G2403, it said that it has some issues with a multi-master transmitting scenario, and so I switched out the MSP430G2403 for MSP430G2553. Even with the new micro controllers, I am still getting the same issues. One thing that is interesting is that when I hook up launchpads together in the same enviroment, even with the buffer chips, it is successful. For some reason I'm having problems on my board, but not the launchpads.

Best Regards,

-Thomas Pinewski