Hi community member,

My customer is considering the following problems and workarounds.

The contents are as follows.

Please tell me about two Questions.

"phenomenon"

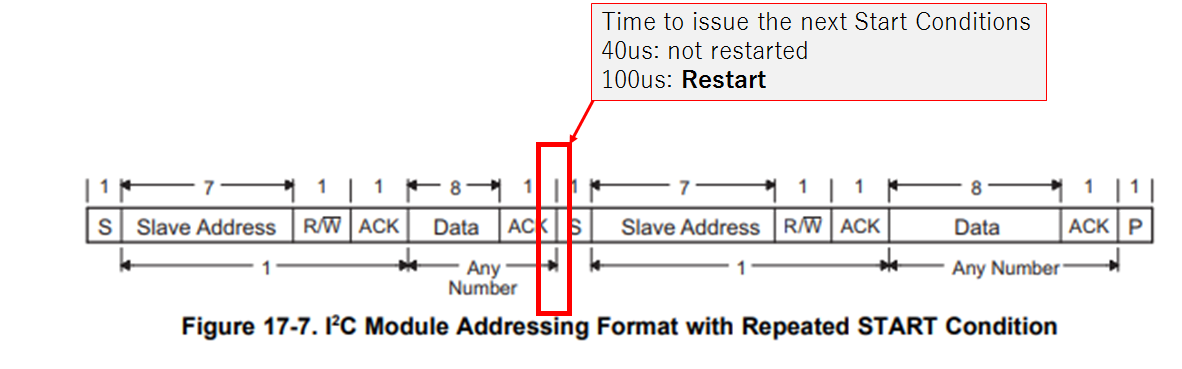

Under the (repeat) start condition of I2C master mode,RESTART is not issued for the following conditions.

· Clock rate: 84 kHz

· ACK before 2nd byte from START Condition Clock stretch is 40us.

Question 1. Do you think this phenomenon applies to Errata's "USCI35"?

"Improvement measures"

The symptoms were improved by the following two methods.

(1) When changing the clock rate to 48kHz, the phenomenon does not occur. (From Workaround of USCI35)

(2) Change ACK before clock stretch of 2nd byte from START condition.

- 40us ⇒ 100us

Question 2. Is the improvement plan of (2) effective?

My customers already introduced MSP430F2254 I2C master mode(repeated start), but fearing that changing the clock rate adversely affects the own entire system.

If (2) is valid, my customers think that they want to incorporate it.

Please let me know some advice!

Best regards.

Cruijff