Other Parts Discussed in Thread: DRV10983, TIDA-01373

Good Morning everybody!

Today I'm here because I noticed two different information in two related user guide for the same device and I really don't know what is the exact one.

Let me explain better what I mean.

I need my processor MSP430FR5972 to control a brushless motor and I want them to communicate via I2C. I use DRV10983 motor driver, so I downloaded and started to study

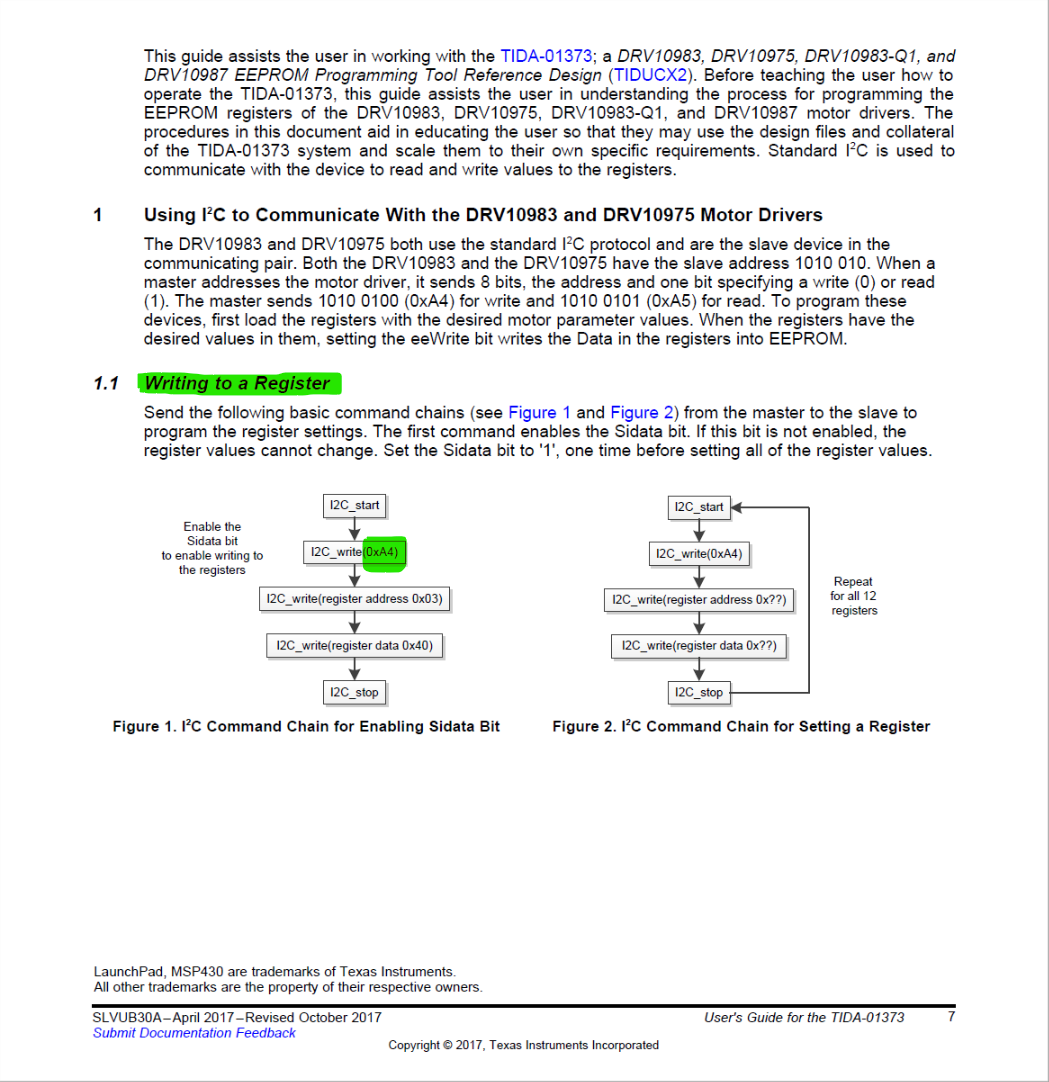

- SLVUB30A --> User's Guide for the TIDA-01373 Quick Start Guide

- DRV10983 12- to 24-V, Three-Phase, Sensorless BLDC Motor Driver Datasheet

In the first chapter of the Quick Start Guide, the first paragraph is about how to write to a register. Below you have the screenshot of the page I'm talking about.

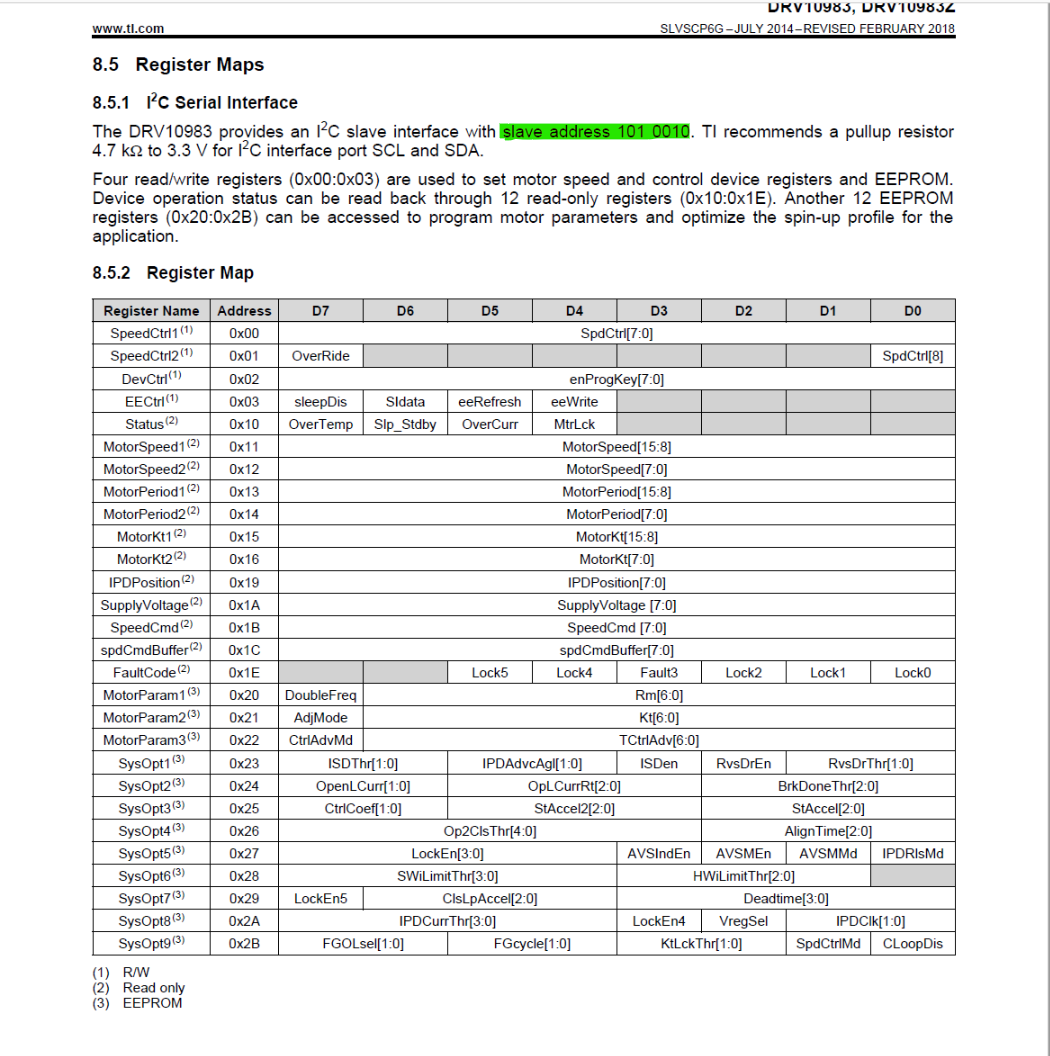

In chapter 8 at paragraph 5 of the datasheet I read:

Which is the right slave address that I have to write?

Thanks & Kind Regards,

MariaAngela