Other Parts Discussed in Thread: MSP430WARE

Tool/software: Code Composer Studio

Hello MSP430 expert,

I've been designing MPPT controller by referring PMP7605 reference S/W using MSP430F5152 MCU.

As Timer D0/D1 is documented that it have problem in using up/down mode to make proper dead time in high resolution mode ,

I tried to synchronize timer D1/D1 using TEC clear command TEC1XCTL2 |=TECAXCLREN & TD0CTL0 |= TDCLR;.

In spite of using the same value to TD0CCTL0/1/2 and TD1CCTL0/1/2, the generated PWM waveform is not synchronized.

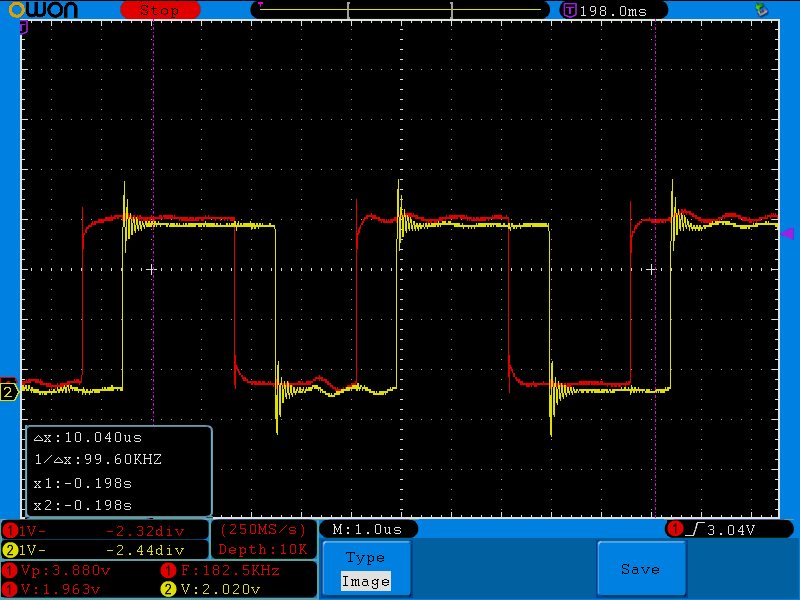

But make about 800nsec timing difference gap as the attached scope capture. The S/W routine is also attached.

Could you pls advise what’s wrong ?

unsigned int Duty =304, Deadtime =25;

{

Get_TLV_Info(TLV_TIMER_D_CAL, 0, &bTD0CAL_bytes, (unsigned int **) &pTD0CAL);

//Get TimerD0 Cal Values (instance 0)

if(bTD0CAL_bytes == 0x0)

{

// No TimerD free running cal data found

while(1); // Loop here

}

// Configure Master Timer Instance - TimerD0, Hi-Res Calibrated Mode

TD0CTL0 = MC_1 + TDSSEL_2; // TDCLK = SMCLK = 25MHz = Hi-Res input clk select

TD0CTL1 |= TD2CMB + TDCLKM_1; // Select Hi-res local clock

TD1CTL0 |= MC_1 + TDSSEL_2; // up-mode,

TD1CTL1 = TD2CMB + TDCLKM_2; // TD1 clock = Auxiliary clock source from master timer instance

TD0HCTL1 = pTD0CAL->TDH0CTL1_128; // Read the 128Mhz TimerD TLV Data

TD0HCTL0 = TDHEN + TDHM_0; // CALEN=0 => free running mode; enable Hi-res mode

TD1HCTL0 = TDHEN + TDHM_0; // CALEN=0 => free running mode; enable Hi-res mode

// Here Timer D is configured to run at 128Mhz

TD0CCR0 = 696; // 1ch TimerD run for non-interleaved

TD0CCR1 = Duty - Deadtime; // High side PW_H1 >> PW_H2

TD0CCR2 = 696 - Deadtime; // Low Side PW_L1 >> PW_L2

TD0CCTL2 |= OUTMOD_7; // TD1CCR2, Set/reset

TD1CCR0 = 696; // 128M/696 = 182.xxKhz is the operating frequency of the buck stage

TD1CCR1 = Duty - Deadtime; //

TD1CCR2 = 696 - Deadtime;

TD1CCTL2 |= OUTMOD_7; //+ CLLD_1; // TD0CCR2, Set/reset

// Syncronize master (TD0) and slave (TD1) timer instances

//

TEC1XCTL2 |= TECAXCLREN; // Enable synchronized clear by enabling Aux clear of slave timer

// TEC0XCTL2 = TECAXCLREN; // Enable synchronized clear by enabling Aux clear of slave timer

TD0CTL0 |= TDCLR; // + TDCLGRP_1; clear TDR, Start timer -UP

// TD1CTL0 |= TDCLR; //+ TDCLGRP_1; TD1CCTL2 = OUTMOD_7 ;//+ CLLD_1;

TD0CCTL2 = OUTMOD_7 ;// + CLLD_1; TD1CCTL1 = OUTMOD_7 + CLLD_1;

Init_IOs ();

}

void Init_IOs (void)

{

P2SEL |= BIT0 + BIT3; // BIT0 // P2.0/TD0.2, P2.2/TD1.1, P2.3/TD1.2, options select

P2DIR |= BIT0 + BIT3 + BIT6 + BIT7; //,

Thanks,

YS Kim