Hi champs,

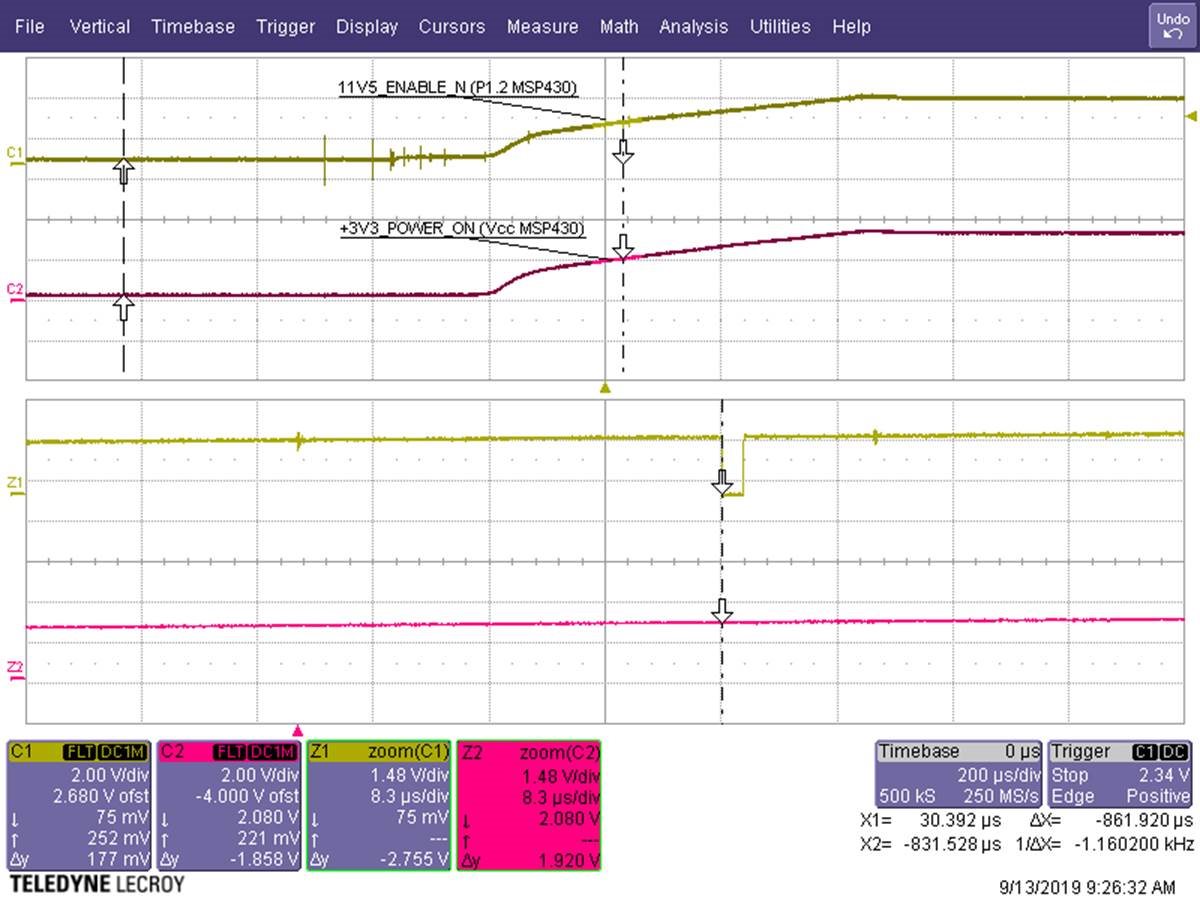

after startup MCU sometimes shows a non expected behaviour (try to get more information from customer).

During this abnormal state, power consumption is significant lower (my not confirmed assumption: CPU clock is much lower than expected).

This behaviour can only be seen without JTAG debugger!

CLK is configured at beginning of code. A workaround seems to insert 2 x __no_operation() to bypass tis behaviour.

Only one __no_operation() does not work secureley!

Customer thought erratum BCL12 can be applied, but code is executed after PON, so very unlikely.

Here is code sequence:

/* Set the MCLK to 12MHz calibrated */

DCOCTL = 0; /* Select lowest DCOx and MODx settings */

BCSCTL1 = CALBC1_12MHZ; /* Set range */

DCOCTL = CALDCO_12MHZ; /* Set DCO step + modulation */

BCSCTL2 |= DIVS_2; /* SMCLK = 3 MHz */

__no_operation();

__no_operation();

Q: Why are 2 x __no_operation() needed and is this a valid workaround to ensure stable execution in mass production ?