Other Parts Discussed in Thread: MSP-FET, AFE4403

Tool/software: Code Composer Studio

Hello,

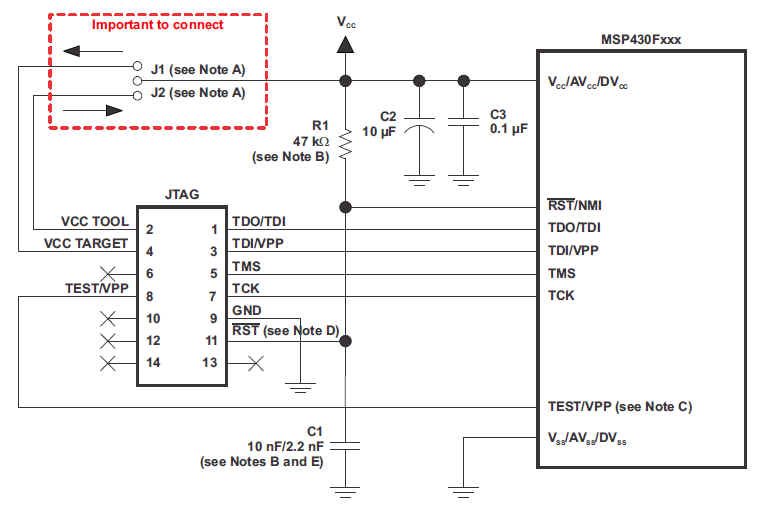

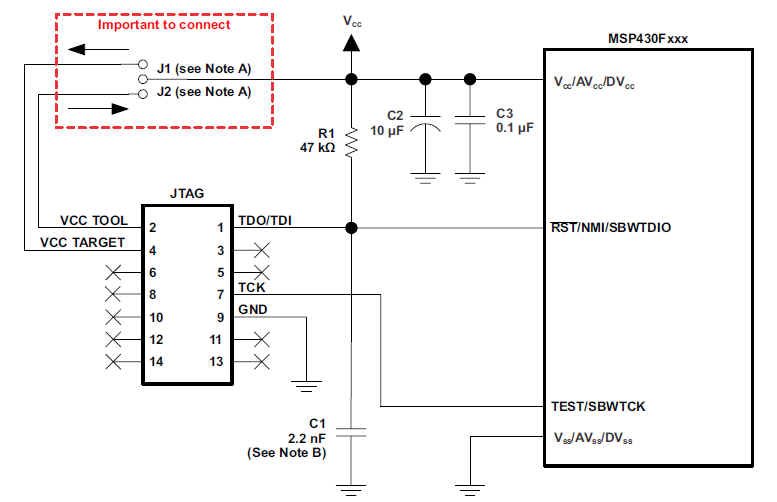

We are actually working on a project and we are going to use the MSP430F6638 MCU. So basically we need a debugger in order to debug the code inside the MSP430F6638. So which debugger do you recommand us to use ? The MSP-FET debugger could be a good solution ? We have taken a look at the MSP debuggers user guide and we found out that we should use a 14-pin JTAG connector with the MSP-FET, right (picture below) ?

Since the MSP430F6638 doesn't have a RTS pin how should we connect pin 13 with the mcu ? Also for the pin 10,12 and 14, in which situation we have to connect these pins to the UART, SPI or I2C pins of the mcu ? In other words pin 10,12 and 14 should be connected to the uart, spi or i2c pins of the mcu ? And finally since the pin 2 (VCC_TOOL) should be connected to the mcu power supply, where pin 4 should be connected ? It's really important for us to be clear with the debug connector connections since it's often source of error.

Thank you.

Best regards,

Mike