Hello,

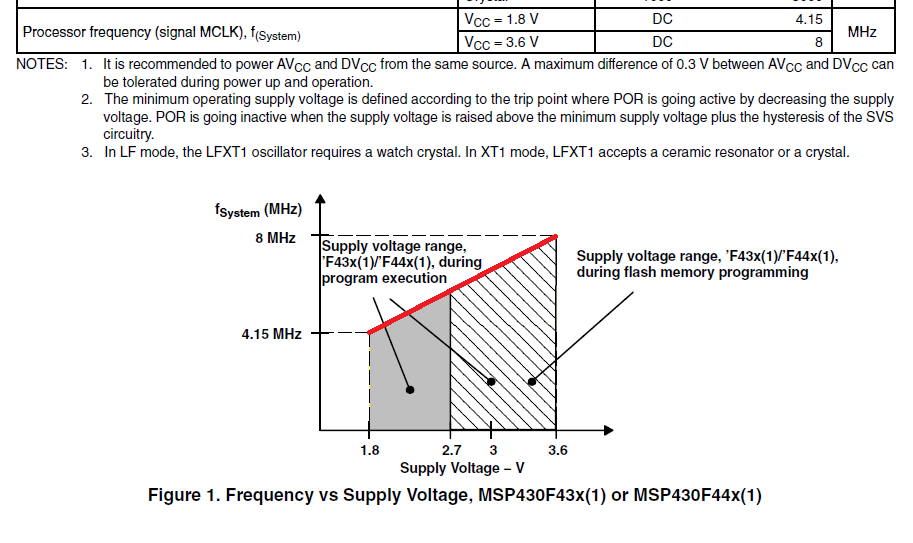

The DS page-37 tells the recommended operating condition for Processor frequency (signal MCLK) f(System). There are a table and the Figure 1.

The Figure 1 has a line between the two points:

(Supply Voltage, fSystem ) = (1.8V, 4.15MHz) and (3.6V, 8MHz).

Then, is it possible to expect the line between the two points are Linear or not ?

As the background, my customer asked me if the CPU works at 8MHz under Vcc=3.3V. We would like to decide the CPU clock frequency under the supply voltage which is not specified.