Hello,

I would like to ask about the failure of MSP430 chip Flash.

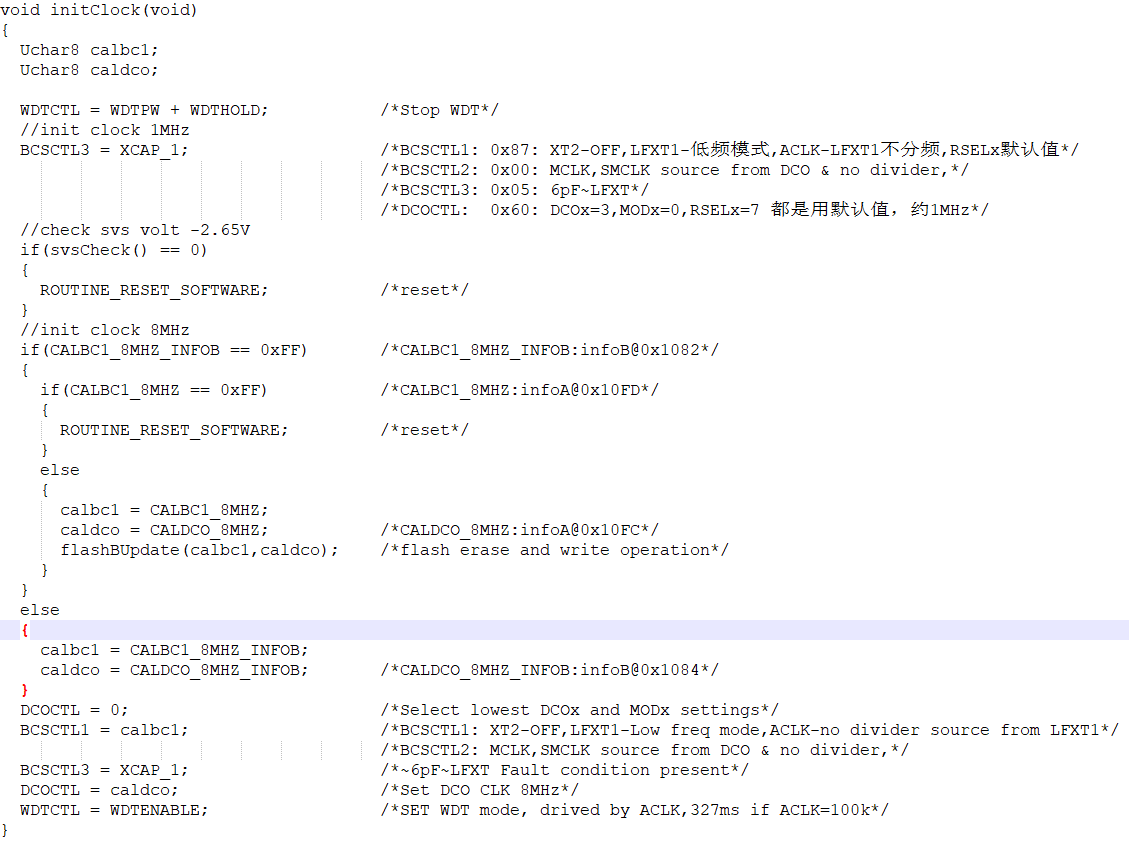

When our chip is powered on, 8MHz clock calibration information (CALBC1_8MHZ_INFOB, CALDCO_8MHZ_INFOB) is backed up in the InfoB Flash area. This calibration information was stored in InfoA (CALBC1_8MHZ, CALDCO_8MHZ). (I know this is a stupid design, but it does exist and causes problems). The clock initialization code after power on is as follows:

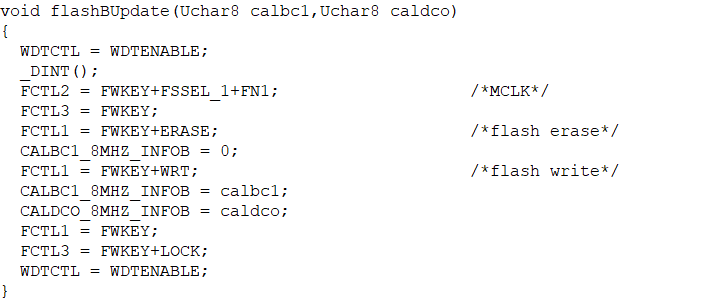

The following is the function to write flash (CALBC1_8MHZ_INFOB, CALDCO_8MHZ_INFOB).

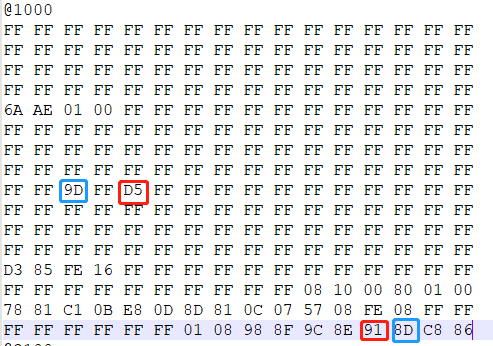

Recently, it was found that some boards (4 to 5 out of 100 boards) work abnormally. Reading flash information through BSL, CALBC1_8MHZ_INFOB, CALDCO_8MHZ_INFOB is inconsistent with CALBC1_8MHZ, CALDCO_8MHZ. There are some bit flips. The specific differences are shown in the figure below:

Now we suspect that one reason may be an error in the flash writing process, an abnormal external tooling or an abnormal power supply, which caused problems in the writing process? Or may static electricity cause problems in the subsequent storage process? However, according to the read flash data, only two flashes in the abnormal board are incorrect, which has certain regularity. So we are more suspicious that the operation of writing flash is caused by an exception, but I carefully reviewed the writing process and failed to find the exception.

Are there any irregularities in our current operations or possible errors? Or what are the possible causes of this abnormality? Thank you.