Other Parts Discussed in Thread: MSP430WARE, MSP430F6736, MSP-TS430PZ100B

Dear Team,

We are designing a poly-phase energy meter and its purely a customised design from your evaluation module. The core part of the circuit remains the same (voltage,current measurement, pin mappings) as it is, but just the output's (display, external communications) were altered.

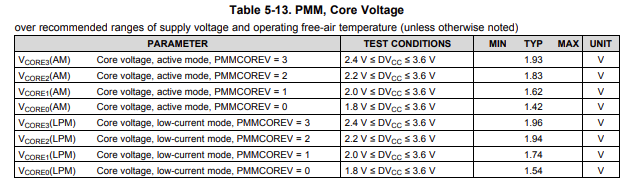

I could get our prototype working, but however i see some troubles with the core voltage. From your sample code i use the below to set the core volltage to 3V, but still see the voltage on (Pin-23 VCORE) is always 1.8V limiting the crystal to 8Mhz. (Controller is powered with 3.3V)

This is the below code that i have picked from your samples. Could you please me if i am missing something ?. Or is the core voltage dependant on some Aux power supply's which we don't focus on at the moment.

Note: At the moment we dont use any Aux supply's and the external 32khz crystal is not mount and left open.

- AuxVCC1&2 are capped to ground

- DVSYS (20&74) connected and capped to ground

- AuxVCC3 left open and external 32khz crystal not mount

void System_Init()

{

PMMCTL0_H = PMMPW_H;

SVSMHCTL&=~SVSMHRRL_7;

SVSMHCTL|=SVSMHRRL_4;

AUX3CHCTL = AUXCHKEY | AUXCHEN | AUXCHC_1 | AUXCHV_1;

AUXCTL0 = AUXKEY;

AUXADCCTL = AUXADC | AUXADCSEL_0 | AUXADCR_0;

AUXCTL2 |=AUX0LVL_6 +AUX1LVL_5 + AUX2LVL_5;

AUXIE |= (AUX0SWIE | AUX1SWIE | AUX2SWIE | AUXSWGIE | AUX0DRPIE | AUX1DRPIE | AUX2DRPIE | AUXMONIE );

PMMCTL0_H = 0;

SetVCore(3);

__bis_SR_register(SCG0); /* Disable the FLL control loop */

UCSCTL6 = (UCSCTL6 | XT1DRIVE_3); /* Highest drive setting for XT1 startup */

while (SFRIFG1 & OFIFG)

{

/* Check OFIFG fault flag */

UCSCTL7 &= ~(DCOFFG | XT1LFOFFG | XT2OFFG); /* Clear OSC fault flags */

SFRIFG1 &= ~OFIFG; /* Clear OFIFG fault flag */

}

UCSCTL6 = (UCSCTL6 & ~(XT1DRIVE_3)); /* Reduce drive to something weaker */

UCSCTL0 = 0;

UCSCTL1 = DCORSEL_6; /* Set RSELx for DCO = 25MHz */

UCSCTL2 = FLLD__4;

UCSCTL2 |= (192 - 1); /* Set DCO Multiplier for 25MHz */

/* Set FLL to 32768*4*192 => 25165824Hz */

__bic_SR_register(SCG0); /* Enable the FLL control loop */

UCSCTL5 |= DIVS__1 | DIVA__32;

UCSCTL4 = SELM__DCOCLK | SELS__DCOCLK | SELA__XT1CLK; /* 24MHz MCLK, 24MHz SMCLK, ACLK (25Mhz/32)*/

__delay_cycles(100);

}

Question-2: Do you have a complete working sample code for the energy meter (https://www.ti.com/tool/EVM430-F67641) ?.

I could access its schematic, but could not directly get the complete working project. i got pieces of code and its too hard to put it together to have a compilable code.

Thanks in advance,

Surya