Hey Everyone,

I have seen a lot of questions about the Brownout Reset (BOR) circuitry and recently ran into it again myself. There are many applications where the BOR works great, but also many applications where the BOR might not be sufficient. This information is all documented, but I'm just trying to bring these resources together.

Background:

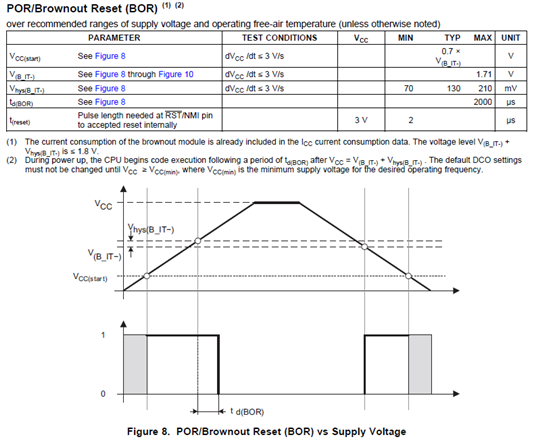

The BOR is a very simple circuit that holds the MSP430 in reset until VCC reaches a threshold voltage. As seen below, in Figure 8, the BOR threshold is max 1.71 V + 210 mV. It has been seen as low as 1.5V. When VCC is rising and reaches this threshold, Reset is released after a small delay, Td(bor), which is max 2ms in this case. There is a time delay to allow VCC to rise to a reasonable voltage before releasing reset. This is what allows the BOR thershold to vary from chip to chip.

When VCC is falling, the BOR puts the MSP430 in reset once VCC hits the BOR threshold without the V_hys added in, so max 1.71V.

Risky Situations:

1. VCC rises slowly

a. BOR can release reset before you are at your expected voltage

2. VCC could dip or VCC falls slowly enough that power could be re-applied before hitting VCC start (MSP430 not fully off)

a. MSP could run an unexpected voltage, before BOR reset. Without power cycle, there could be potential problems.

Potential Problem:

Mclk vs VCC: This violation is when running the DCO at a frequency with a minimum required VCC, while that VCC condition is not met. When this happens, the MSP is being run in violation to specifications, and no operation is garenteed. I'm going to include a list of issues that this violation has been seen to cause, but it's not exclusive.

Observed issues: Issues with Async communication, Incorrect Read/Writes, Flash Corruption, DCO locks/MSP430 won't run, etc.

Solution:

It falls to the user to make sure there are no specification violations. If you believe your application falls in the Risky Situations above, I would recommend either an MSP430 with a built in Supply Voltage Supervisor (SVS) or an external Voltage supervisor like the TPS3803.

FAQ:

(Q1) The datasheet doesn't specify anything running below 1.8V. What happens if the BOR releases and VCC is only, lets say, at 1.7V?

(A1) Code execution will proceed as expected, provided MCLK stays at the default DCO freq. However, any peripheral operation is not garunteed untill the VCC requirments for that pheripheral are met.

Related Post: http://e2e.ti.com/support/microcontrollers/msp43016-bit_ultra-low_power_mcus/f/166/p/19070/73890.aspx#73890

Thanks!

JD