Hi i'm keep seeing glitch or spike on i2c data.

Settings are:

- Pull up Resistor: 10k / Series Resistor: 250 Ohm

- Master Tx and Rx : MSP430F1611 USART I2C , I2CCLK = SMCLK = XT2 Crystal 7.3728MHz, I2CPSC = 0, I2CSCLH = 0x20 / I2CSCLL = 0x20 to generate ~100kbps SCL

- Slave Rx and TX: MSP430F2132 USCI I2C, I2CCLK = SMCLK = DCO ( does slave clk setting matter?) but set to generate ~100kbps SCL as well.

- SW: Master writes 8 bytes to slave and read the same data to verify. If the data is different 1611 board LED toggles.Master and Slave code only does I2C handling via ISR.

And these are images of spikes:

from the saleae logic analyzer:

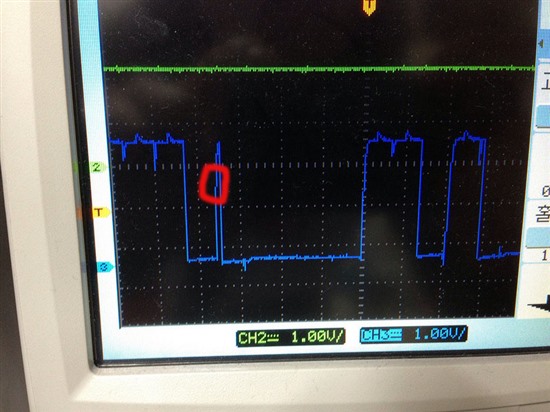

from the oscilloscope:

It looks like the spike is not affecting the data value as the spike is not on valid SDA timing.

but i'm worried that spike might induce wrong data format in more noisy situation.

Anyone knows why the spike are generated ? and how to get rid of them?

I've communicated to TMP102 temp sensor but still seeing the spike.

I wonder whether this is some intrinsic issue on shift-out or shift-in of msp430 i2c modules?