We have been using the MSP430F5515 in production and have begun to run into serious problems with the USCI in UART mode. The UART bit time errors seem to vary significantly more than they should. Can a TI employee verify that there is not a silicon problem with the UART?

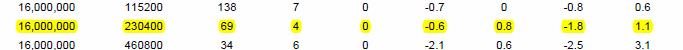

Here are our parameters:

UART BRCLK is sourced from MCLK which is derived from a 32.768khz crystal. Crystal frequency has been measure at 32768Hz exactly.

MCLK is initialized to 16MHz has been measured at 15.997MHz.

UART buad rate is set to 230400 using UCOS16=0 to minimize the calculated potential bit errors. From the Family User Guide (SLAU208M)

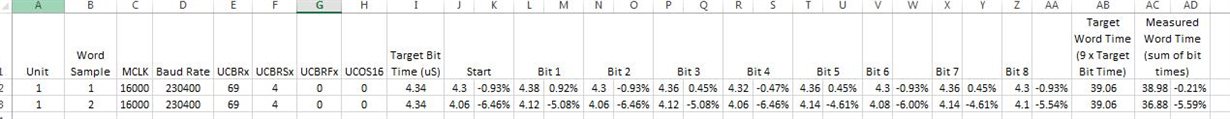

As a test we send a series of sixteen 0xAA bytes from the MSP to a DSP (TMS320C5515). The results are show below:

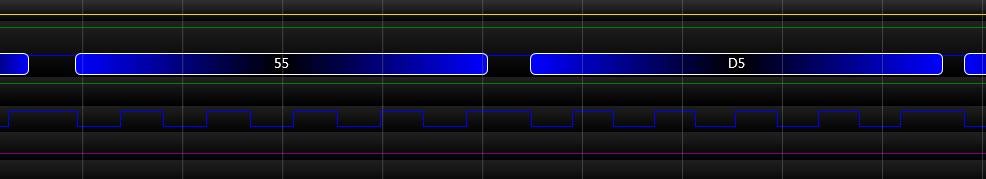

The test shows two consecutive 8-bit words from our test sequence.

The first word (Unit 1, Word Sample 1) is sent and received correctly. The cumulative bit time error is -.21% which is acceptable.

The second word (Unit 1, Word Sample 2) is sent as a 0x95 instead of 0x55 since the cumulative bit time is 5.59% too short. Below is a screen shot of the two consecutive words.

It is clear from our tests that the bit times generated by the MSP430 are inaccurate and vary from word to word. This "short word" happen sporadically and at with varying recurrence of different chips.

Can someone from TI please investigate this issue and get back to me asap?

Or if someone can see something we are doing wrong, please let us know.