Team,

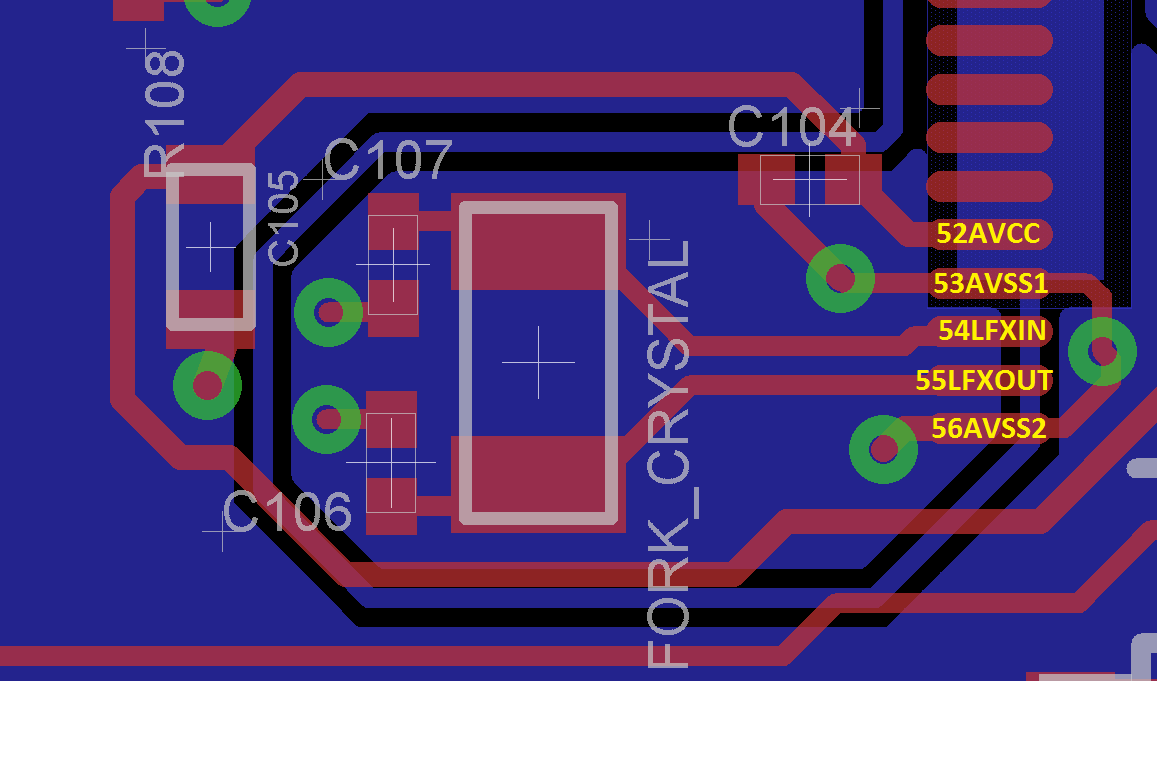

we have problems with fork crystal for MSP430FR6922. We need to set 8MHz for MCLK and set fork external crystal to ACLK.

Below you can see the function we use, If we use it, MSP430FR6922 stays in loop do - while for a few seconds. That time is random, ranging between 1 sec and infinity.

Parameters of crystal are:

- Package: 3215

- Load capacitance: 6pF

- Frequency: 32768 Hz

Can you please advise what's the issue, or where's a mistake in the code?

One remark is that if we work with msp430fr6922 on jtag programmer, described problem will not happen. If we unplug this and connect to 3V source, described problem will begin.

Thank you for your help.

TI Customer

void ClocksStart(void)

{

PJSEL0 |= BIT4 | BIT5; // Enable clock function pin for crystal.

// Disable the GPIO power-on default high-impedance mode to activate

// previously configured port settings

PM5CTL0 &=~LOCKLPM5;

SFRIE1 &=~ OFIE; //Block interrupts that occur when a crystal error occurs

// Setup Clocks

CSCTL0_H = CSKEY >> 8; // Unlock CS registers

CSCTL1 = DCOFSEL_6; // DCORSEL = 0 a

DCOFSEL=6 (DCOFSEL=110)-> 8MHz

CSCTL4 &= ~ LFXTDRIVE_2; // Set the power to the crystal, LFXTDRIVE 00 - 3,5 pF, LFXTDRIVE 01 - 6 pF,LFXTDRIVE 10 - 9 pF, LFXTDRIVE 11 - 12 pF

CSCTL2 = SELA__LFXTCLK | SELS__DCOCLK | SELM__DCOCLK; // set ACLK = XT1; MCLK = DCO

CSCTL3 = DIVA__1 | DIVS__1 | DIVM__1; // Set all dividers to 1

CSCTL4 &= ~LFXTOFF; // Enable crystal.

P9DIR |= BIT5;

do

{

P9OUT ^= BIT5;

CSCTL5 &= ~LFXTOFFG; // Clear XT1 fault flag

SFRIFG1 &= ~OFIFG;

} while (SFRIFG1 & OFIFG); // Test oscillator fault flag

CSCTL0_H = 0; // Lock CS registers

SFRIE1 |= OFIE; //Allow interrupt that occurs when a crystal error occurs }