Dear colleagues,

I'm using the ADC embedded into the MSP430FR5969 operating at low frequency in LPM3.

Then I'm trying to transfer the result of the conversion via DMA to a given memory position.

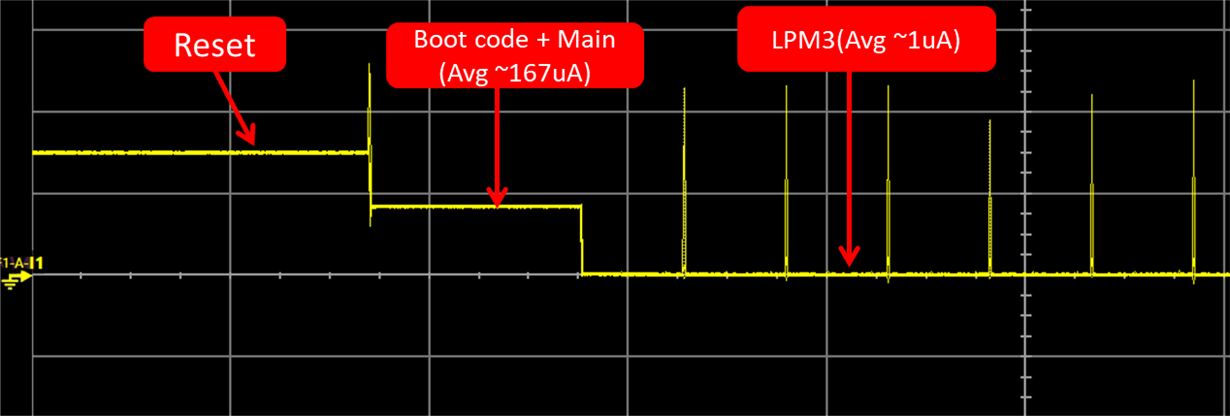

However, I have a problem with the resulting LPM after employing the DMA.

I thought that the MCU would get back to LPM3 after transferring the data, but it stays in LPM0.

Is that what we should expect or I'm doing something wrong in the configuration?

Many thanks in advance,

Ferran