Tool/software: Code Composer Studio

Hello,

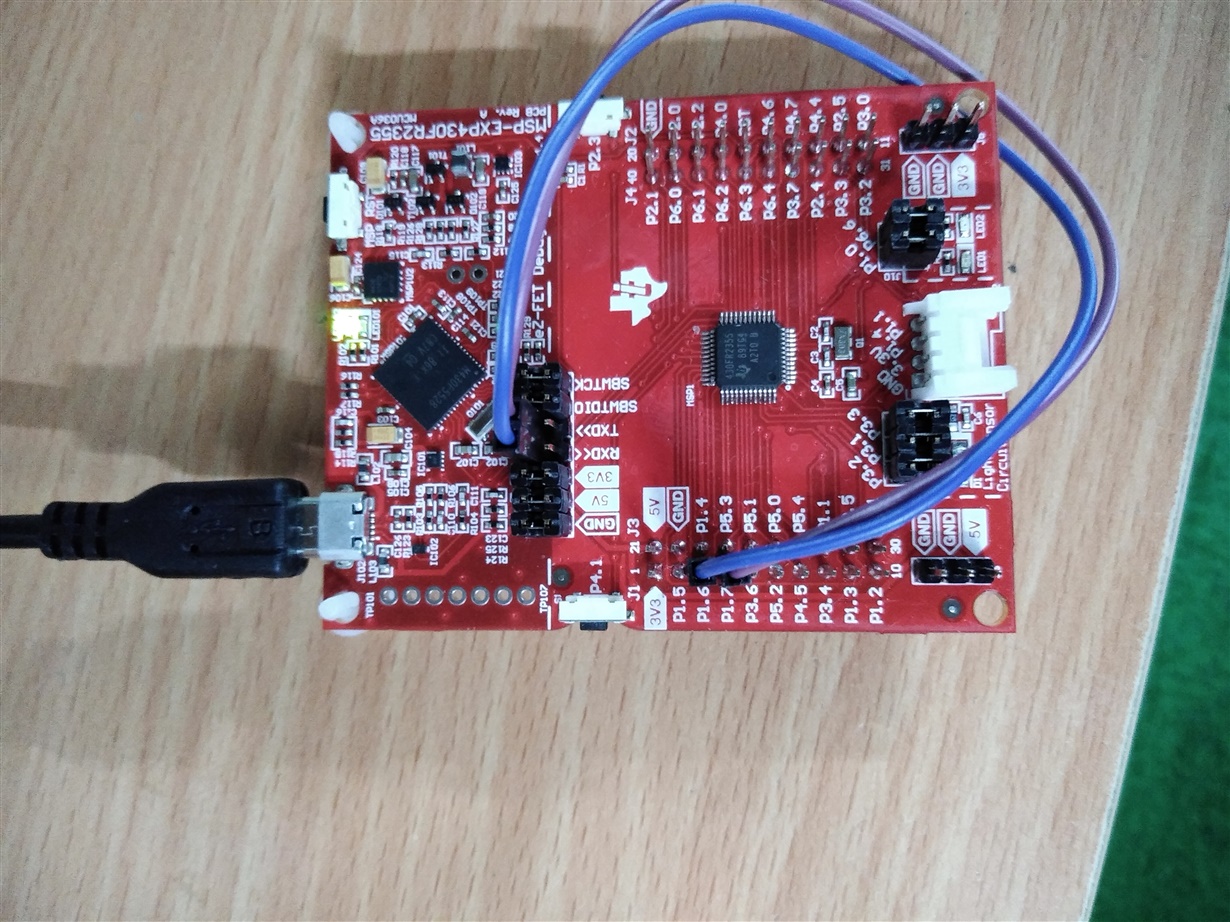

I am trying to connect MSP430FR2355 with my PC through UART communication to echo characters entered by me through keyboard. I copied example code msp430fr235x_euscia0_uart_01.c from TI resource explorer to CCS v8 on my PC. As given in description,I should get echo of characters entered by me on CCS terminal but this is not working for me. Cursor is blinking but I am unable to enter any character on terminal.

Regards