Dear TI Team,

We have a design which uses MSP430AFE253. But we encountered a strange POR reset issue as the MCU occasionally failed to properly reset itself , thus prevents it from running firmware application. However, when we physically shorted RST pin to ground as soon as we observed MCU reset failure, the MCU resumes working again. I included below information for you reference. Would you please kindly review our design and check if there is any potential cause to the reset issue that we have been experiencing? Thank very much for your help.

1) Figure 1 -schematic design,

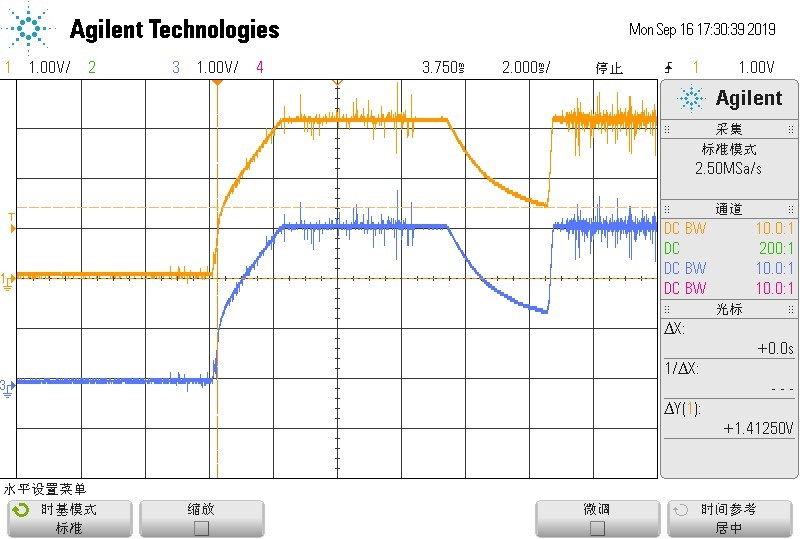

2) Figure 2 - Waveform capture for MCU_VCC/RST pins

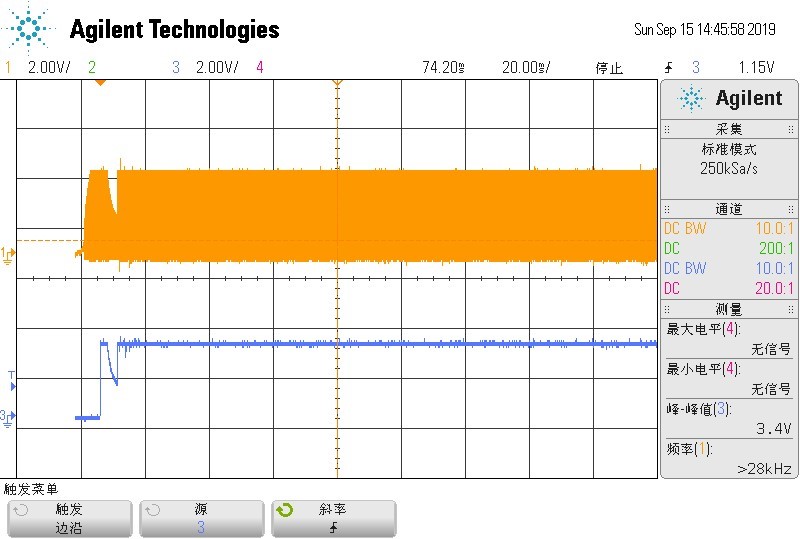

3) Figure 3 - Waveform capture for crystal output.

4) Crystal data sheet

Best regards,

Peter

Figure 1: MSP430AFE253 Schematic

Figure2 : Scope Capture - MCU-VCC (Orange color) / MCU-RST (Blue color)

Figure 3: Crystal output (Orange Color)