Other Parts Discussed in Thread: MSP430F148

Team,

we are prototyping with I2021 and have a few questions,

We will use external resistor for the oscillator. The tolerance of the resistor recommended in the datasheet is 0.1%, but in practice it's possible we'll have a resistor with slightly different value / a bit worse tolerance. As a consequence we will need to calibrate the frequency and memorize the CSERFCAL register value.

- What is the meaning of each register bits? Alternatively, how to calibrate the frequency (by +/- few percent range)?

- We assume we can measure the MLCK frequency (directly or its subdivision) and change the value in CSREFCAL through serial interface.

- From different reasons we would prefer to use 16MHz instead of 16,384MHz clock. This yields the clock of the a/d converter of 1MHz, instead of the recommended 1.024MHz.

- Can it impact negatively and visibly the operation of the converter and of the whole device?

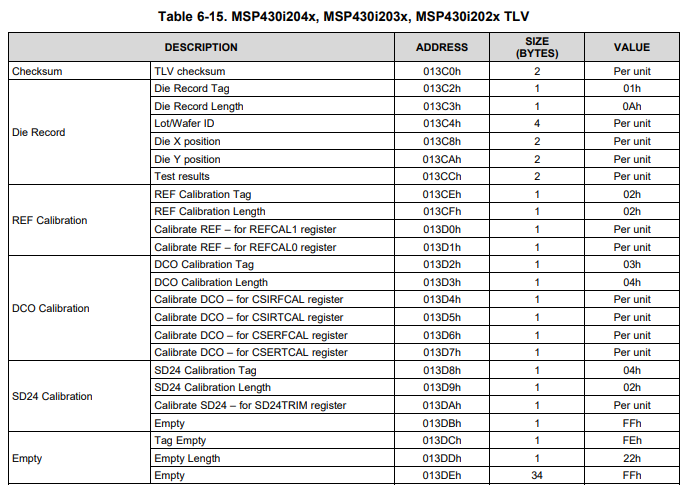

- Do MSP430i20xx have in their primary memory any identifiers that would help to identify them? If so, where/how?

- For example, MSP430F148 has 0xf149 under 0x0ff0 address.

Thank you.