Other Parts Discussed in Thread: MSP-EXP430F5529LP,

Hello,

Could you please advise about the following glitch?

Q1. Is it a known phenomenon for the part?

Q2. Do you think this glitch will be harmful under any conditions to induce a communication error ? My customer is afraid of that the glitch form or timing changes.

My customer uses one of the USCI as I2C master at 380kHz.

They found a glitch on the SDA when the SCL falls as a start condition.

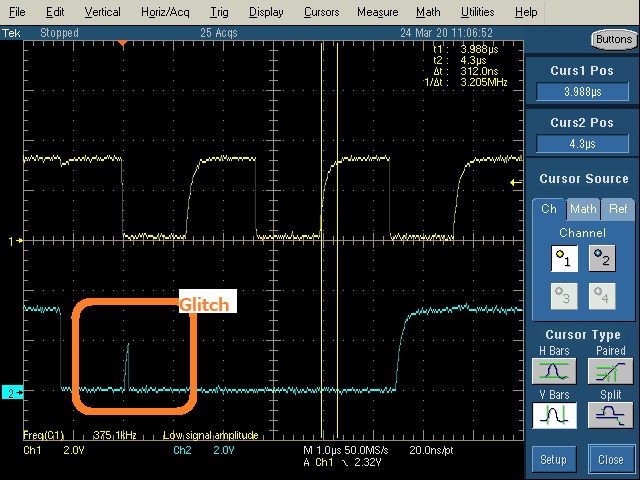

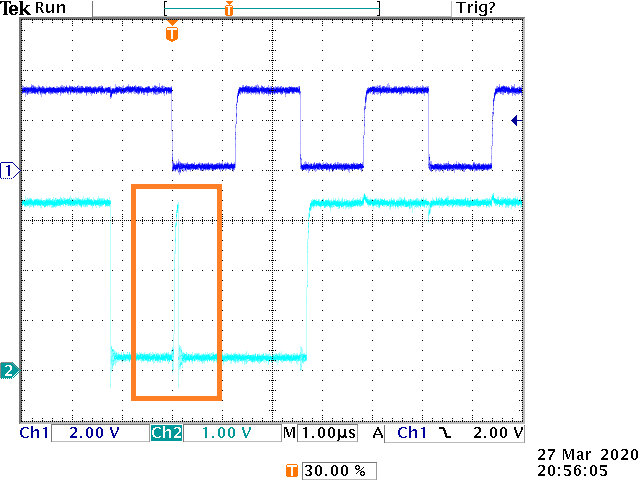

An oscilloscope screen was provided as below. Ch1(upper) = SCL, Ch2(Lower) = SDA.

Please find the glitch on the Ch2 = SDA right after the first falling edge of the SCL.

I found a thread which looks close to this phenomenon:

https://e2e.ti.com/support/microcontrollers/msp430/f/166/t/237128