Other Parts Discussed in Thread: CAPTIVATE-FR2676, CAPTIVATE-PGMR, , MSP430FR2476

Good Morning,

I have to be missing something so simple! I know will feel dumb when someone shows me what I missed - but at this point - I can take it!!

- Any help will be so much appreciated :)

QUESTION:

- What dumb setting am I missing?

SYMPTOM:

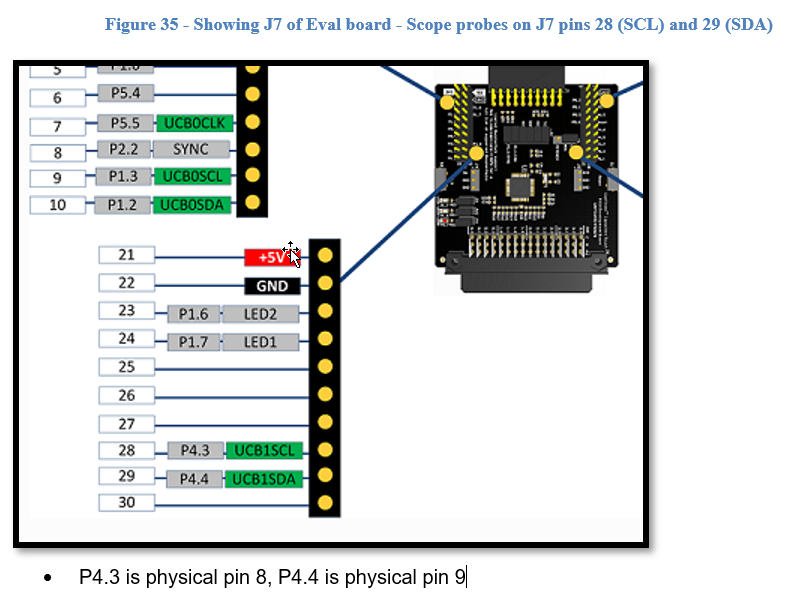

- Have scope on P4.3 (SCL) & P4.4 (SDA) of CAPTIVATE-FR2676 Eval board (J7 pins 28 & 29)- and NEVER see any activity (yes my scope is set up correctly LOL)

INFO:

- I am using CCS, with the CAPTIVATE-PGMR & CAPTIVATE-FR2676 Eval board (MSP430FR2676TPTmicro - 48 LQFP package).

- No Slave is attached but configuring as Master so should still see something

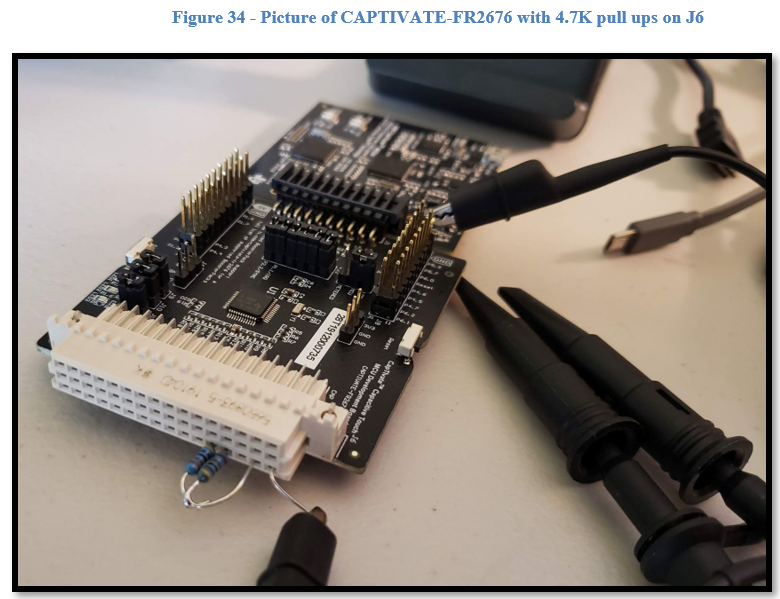

- Have external 4.7K ohm pull ups on SCL and SDA

- I used Example code MSP430FR267x_euscib0_i2C_15 as starting point: (Master Code)

- Again want as master – so can see sending out Slave Address

- The example uses euscib0.

- Changed code to uses euscib1 (so exposed on J7 header of Eval board – can scope)

- Changed PxSEL registers to use P4.3 (CLK) and P4.4 (SDA) so again can scope.

- Those were the only changes made!!

- I did NOT try the Example code right out of box – since believe the Programmer board is using to program the MSP430.

Again – can’t thank you enough – pull what little hair left on my head out!!

Willie

----------------------------

--------------------

Actual Code:

// MSP430FR267x Demo - eUSCI_B0 I2C Master TX bytes to Multiple Slaves

//

// Description: This demo connects two MSP430's via the I2C bus.

// The master transmits to 4 different I2C slave addresses 0x0A,0x0B,0x0C&0x0D.

// Each slave address has a specific related data in the array TXData[].

// At the end of four I2C transactions the slave address rolls over and begins

// again at 0x0A.

// ACLK = REFO = 32768Hz, MCLK = SMCLK = default DCO = ~1MHz

// Use with msp430fr267x_eUSCIB_04.c

//

// /|\ /|\

// MSP430FR2676 10k 10k MSP430FR2676

// slave | | master

// ----------------- | | -----------------

// | P1.2/UCB0SDA|<-|----|->|P1.2/UCB0SDA |

// | | | | |

// | | | | |

// | P1.3/UCB0SCL|<-|------>|P1.3/UCB0SCL |

// | | | P1.0|--> LED

//

// Longyu Fang

// Texas Instruments Inc.

// August 2018

// Built with IAR Embedded Workbench v7.12.1 & Code Composer Studio v8.1.0

//******************************************************************************

#include <msp430.h>

unsigned char TXData[]= {0xA1,0xB1,0xC1,0xD1}; // Pointer to TX data

unsigned char SlaveAddress[]= {0x0A,0x0B,0x0C,0x0D};

unsigned char TXByteCtr;

unsigned char SlaveFlag = 0;

int main(void)

{

WDTCTL = WDTPW | WDTHOLD; // Stop watchdog timer

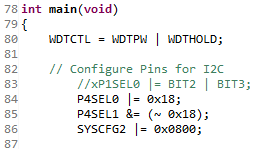

// Configure Pins for I2C

//xP1SEL0 |= BIT2 | BIT3; // I2C pins

P4SEL0 |= 0x18; // configure I2C pins (device specific)

P4SEL1 &= (~ 0x18); //Using Physical pins 8,9 of MSP430FR2676TPT (48 LQFP package on Captivate MSP430FR2676 Eval board)

// Disable the GPIO power-on default high-impedance mode

// to activate previously configured port settings

PM5CTL0 &= ~LOCKLPM5;

// Configure USCI_B0 for I2C Master Mode

UCB1CTLW0 |= UCSWRST; // put eUSCI_B in reset state

UCB1CTLW0 |= UCMODE_3 | UCMST | UCSYNC; // I2C master mode, SMCLK, UCA10 = 0 by default from reset

UCB1BRW = 0x8; // baudrate = SMCLK / 8

UCB1CTLW0 &=~ UCSWRST; // clear reset register

UCB1IE |= UCTXIE0 | UCNACKIE; // transmit and NACK interrupt enable

SlaveFlag =0;

while(1)

{

__delay_cycles(1000); // Delay between transmissions

UCB1I2CSA = SlaveAddress[SlaveFlag]; // configure slave address

TXByteCtr = 1; // Load TX byte counter

while (UCB1CTLW0 & UCTXSTP); // Ensure stop condition got sent

UCB1CTLW0 |= UCTR | UCTXSTT; // I2C TX, start condition

//(***** Expect to see some I2C clock signals on scope - but DON'T :( )

// __bis_SR_register(LPM0_bits | GIE); // Enter LPM0 w/ interrupts

// Remain in LPM0 until all data

// is TX'd

// Change Slave address

SlaveFlag++;

if (SlaveFlag>3) // Roll over slave address

{

SlaveFlag =0;

}

}

}

#pragma vector = EUSCI_B1_VECTOR

__interrupt void USCI_B1_ISR(void)

{

switch(__even_in_range(UCB1IV,USCI_I2C_UCBIT9IFG))

{

case USCI_NONE: break; // Vector 0: No interrupts break;

case USCI_I2C_UCALIFG: break;

case USCI_I2C_UCNACKIFG:

UCB1CTL1 |= UCTXSTT; //resend start if NACK

break; // Vector 4: NACKIFG break;

case USCI_I2C_UCSTTIFG: break; // Vector 6: STTIFG break;

case USCI_I2C_UCSTPIFG: break; // Vector 8: STPIFG break;

case USCI_I2C_UCRXIFG3: break; // Vector 10: RXIFG3 break;

case USCI_I2C_UCTXIFG3: break; // Vector 14: TXIFG3 break;

case USCI_I2C_UCRXIFG2: break; // Vector 16: RXIFG2 break;

case USCI_I2C_UCTXIFG2: break; // Vector 18: TXIFG2 break;

case USCI_I2C_UCRXIFG1: break; // Vector 20: RXIFG1 break;

case USCI_I2C_UCTXIFG1: break; // Vector 22: TXIFG1 break;

case USCI_I2C_UCRXIFG0: break; // Vector 24: RXIFG0 break;

case USCI_I2C_UCTXIFG0:

if (TXByteCtr) // Check TX byte counter

{

UCB1TXBUF = TXData[SlaveFlag]; // Load TX buffer

TXByteCtr--; // Decrement TX byte counter

}

else

{

UCB1CTLW0 |= UCTXSTP; // I2C stop condition

UCB1IFG &= ~UCTXIFG; // Clear USCI_B0 TX int flag

__bic_SR_register_on_exit(LPM0_bits); // Exit LPM0

}

break; // Vector 26: TXIFG0 break;

case USCI_I2C_UCBCNTIFG: break; // Vector 28: BCNTIFG

case USCI_I2C_UCCLTOIFG: break; // Vector 30: clock low timeout

case USCI_I2C_UCBIT9IFG: break; // Vector 32: 9th bit

default: break;

}

}