Team,

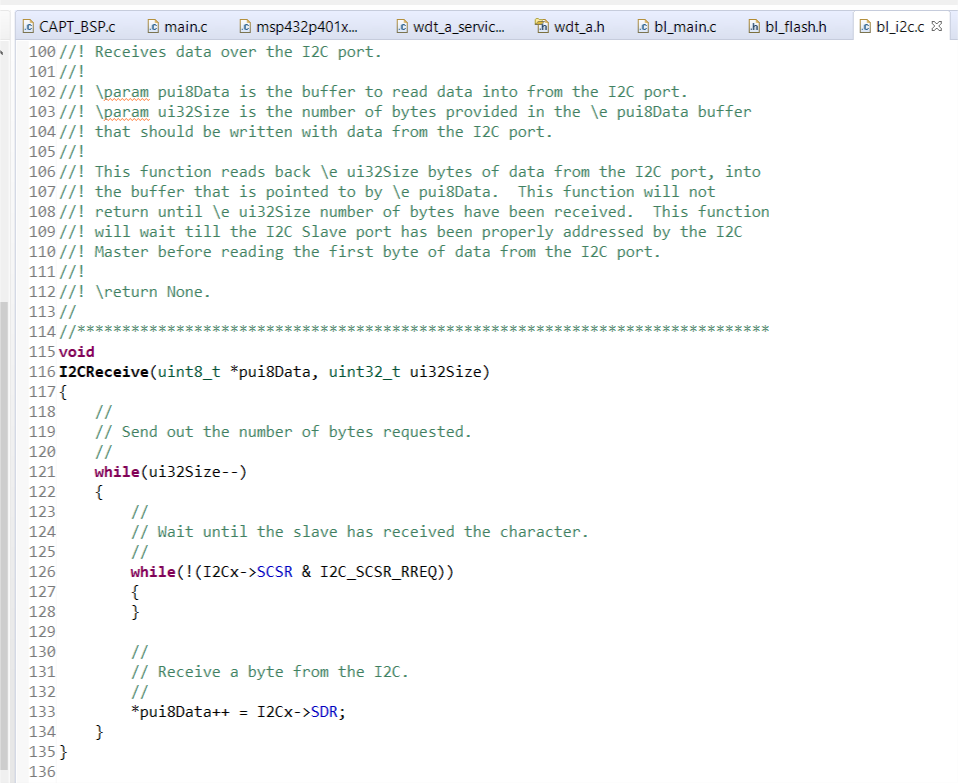

I am trying to determine if the MSP432's dedicated I2C block will support a register read initialized with one master byte (i.e. master sends slave address with read request, and slave data immediately follows) or two master bytes (i.e. master sends slave address with read request, then the register address, and slave data immediately follows).

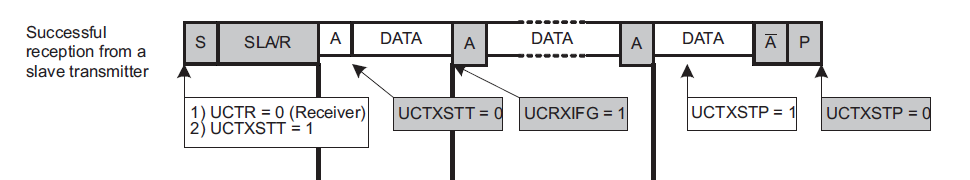

I know the standard typically requires three master bytes (0:write request, 1:slave address, 2:read request) to be sent before the slave starts to respond as shown in Figure 9 of http://www.ti.com/lit/pdf/slva704. However, looking through the "UM10204 I2C-bus specification and user manual" from NXP ( https://www.nxp.com/docs/en/user-guide/UM10204.pdf ), I found that there is a mode whereby the "Master reads slave immediately after first byte (see Figure 12). At the moment of the first acknowledge, the master-transmitter becomes a master-receiver and the slave-receiver becomes a slave-transmitter."

However, I have not been able to find any mention or examples (from TI and non-TI sources) that implement this single master byte initiated register read, so I assume it is not very common. I know the I2C supports the Quick Command in SMBus mode, which is similar, but not identical to what is described in the I2C standard doc. Figure 1 of the http://www.ti.com/lit/an/sloa132/sloa132.pdf shows a comparison SMBus versus I2C, and it is the "I2C Single -Byte Read" (top right) example in the figure we want to implement using the I2C block of the MSP432 without having to bit-bang.

If the MSP432E401Y's I2C block only supports the 3 byte master initiated register read, does TI offer an alternative MCU that does support the 1 or 2 byte master initiated standard variant? If not, I suspect this will need to be bit-banged.