Flash charge retention is the ability of the flash cell to retain its programmed value during long-term storage. Here, "programmed" means logic 0?

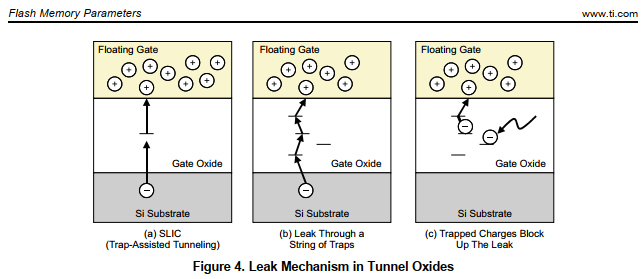

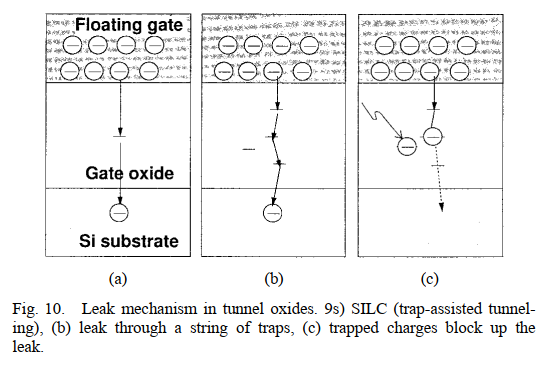

But I'm confused by the descriptions below, e.g. "leakage only can flip an erased cell with the logic level 1 to a programmed cell with the logic level 0".