Part Number: MSP432P401M

Hello,

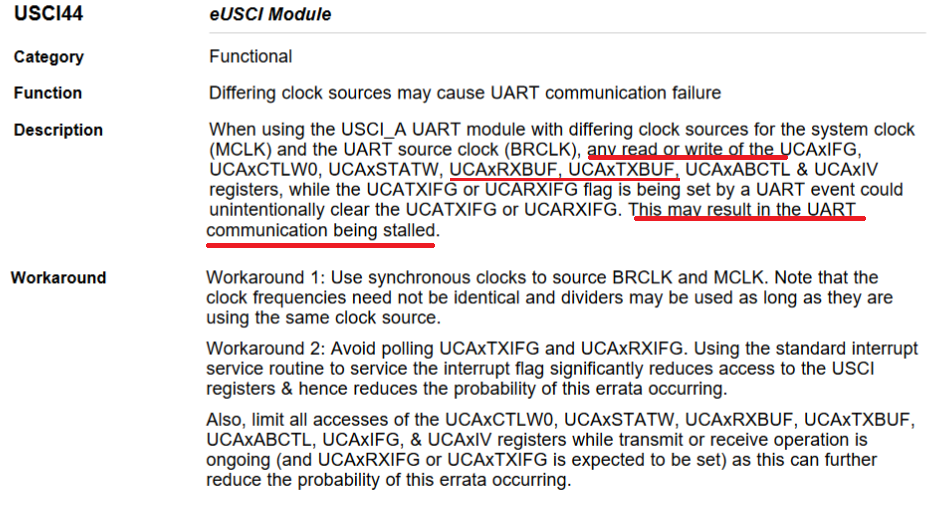

I have a question for USCI44 errata in MSP432P401M.

The errata says using interrupt can reduce the probability of this problem.

When using DMA for both TX and RX, can this USCI44 be completely avoided?

Regards,

Oba

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: MSP432P401M

Hello,

I have a question for USCI44 errata in MSP432P401M.

The errata says using interrupt can reduce the probability of this problem.

When using DMA for both TX and RX, can this USCI44 be completely avoided?

Regards,

Oba

Oba,

you should prevent read or write instructions to the mentioned registers in the ERRATA while UART TX or RX flags can be set. Therefore polling is a problem because you access the registers all the time and the chance is high to hit the raise condition.

It is mentioned that with interrupts the probability is significantly reduced because the register accesses are reduced. Therefore the answer to your questions is: it depends? If the condition to access the register during UART flag setting is prevented with your solution it should be avoided.

Hello Dietmar,

Thanks for your answer.

So if CPU doesn’t access these registers and only DMA accesses UCAxRXBUF and UCAxTXBUF, this problem never happen. Correct?

My customer would like to know how likely this problem occurs. Do you know the probabitliy?

Also does it depend on its environment like temperature and VCC voltage?

Regards,

Oba

Hi Oba,

If the flags trigger the DMA access which finally access the register and in the meantime no other register accesses appear it should be fine.

Probability numbers are not available and yes temp an supply affect it but also here no numbers are available.

Hello Dietmar,

Thank you very much for your answer.

So DMA access these registers(actually only UCAxRXBUF and UCAxTXBUF) is no problem.

The problem here is just CPU access to these registers. Correct?

Regards,

Oba

Oba,

it doesn't matter if DMA or CPU access thats not the point but when you use DMA it is triggered by the flags so it normally would not access while a flag is set that's the point. And for sure you should not access these registers somehow in between as well.

To give you a negative example.

If you trigger the DMA via Timer to read data from RXBUF to RAM it still can happen that the RXFLAG is set while you access the register. So same scenario as for CPU.

Hello,

OK, I understand both DMA access and CPU access could cause the problem.

But sorry, I can’t understand the point of your negative example.

When DMA is requested by the flag, is the flag automatically cleared before the DMA ch actually access the RX/TXBUF?

So when a DMA ch triggered by the flag, the flag usually is cleared and this DMA access should be no problem.

But if a DMA ch triggered by other resources, the flag could be set and could be cleared by this errata?

Is that what you want to mention?

The errata says that UCAxRXBUF and UCAxTXBUF access also could cause this problem.

Does it mean accessing UCAxRXBUF could clear UCATXIFG and accessing CUAxTXBUF clear UCAxRXIFG?

And if these flags are cleared by this errata, are the triggered DMA by the flag and triggered interrupt by the flag which are not served yet canceled?

Regards,

Oba

Oba,

sorry maybe my explanation was not perfect but you got the point! So if you handle it as you described in the first 3 lines I don't see a huge risk.

As said using interrupts will lower the probability significantly and with the solution you plan I don't see a huge risk.

Hello Dietmar,

Could you please answer the below two questions?

The errata says that UCAxRXBUF and UCAxTXBUF access also could cause this problem.

Does it mean accessing UCAxRXBUF could clear UCATXIFG and accessing CUAxTXBUF clear UCAxRXIFG?

And if these flags are cleared by this errata, are the triggered DMA by the flag and triggered interrupt by the flag which are not served yet canceled?

Regards,

Oba

Oba,

I think your questions are already answered by the ERRATA text. If the flags get cleared by this ERRATA transmission can be stalled means the flags gets not serviced because they were cleared. I think this is what the ERRATA describes.

This can appear by any write or read to the registers listed in the ERRATA.

**Attention** This is a public forum