Other Parts Discussed in Thread: MSP430F6733A, MSP-TS430PEU128

Hi experts,

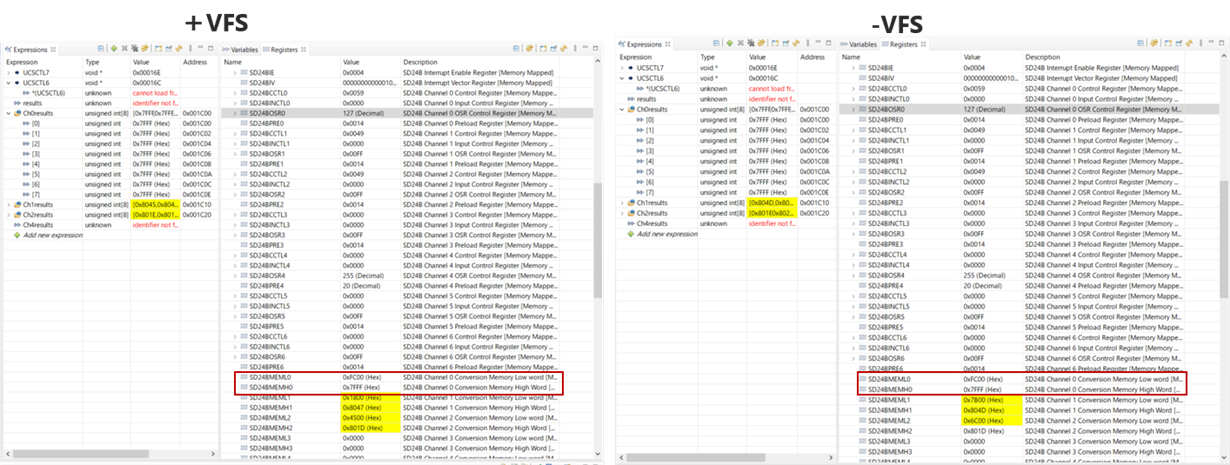

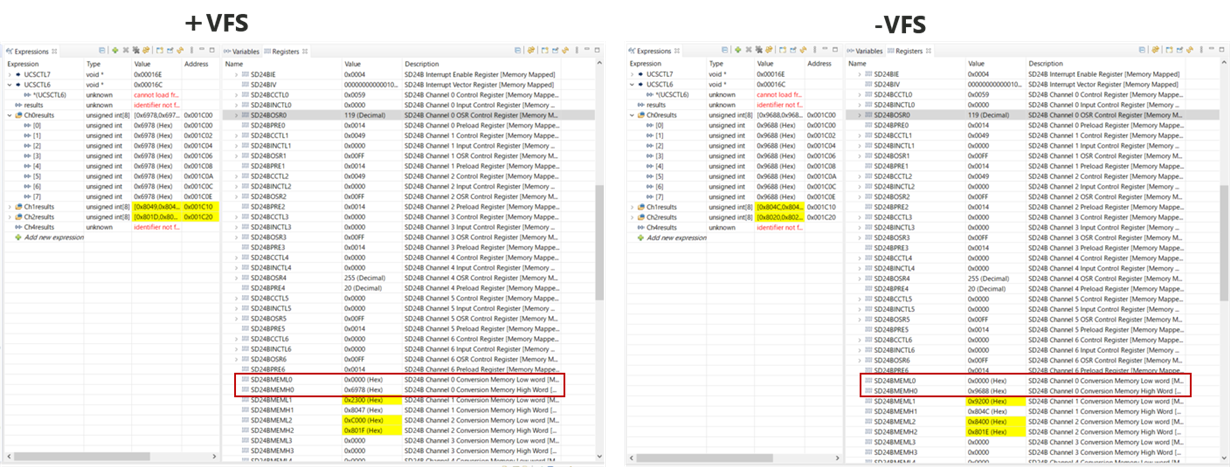

My customer has created two custom sensor boards using MSP430F67719A and MSP430F6733A. Due to the board, there is a case where -VFS (about -1.2V or more) is input to SD24, but SD3 problem occurred because the result is output in two complement mode. The phenomenon is that the result value of +VFS (above about +1.2V) and -VFS (above about -1.2V) are the same. My customer and I have read the errata and know that there is no workaround and that the problem does not occur when using the offset binary mode.

However, according to the customer's research, when the +VFS and -VFS results are far apart, such as when OSR=120, this problem does not seem to occur. To add a little more, the problem seems to occur when the difference between the +VFS and -VFS data results is "1", such as when OSR=128 or 256. I have confirmed the above myself using MSP-TS430PEU128 and F67791A.

Q1: When using two complement mode, can I consider it effective if I set the OSR value such that the difference between +VFS and -VFS is more than 1 (e.g. OSR=120)?

Errata says that the output result will be incorrect regardless of all OSR values and any alignment.

I know that the voltage range that I am inputting in the first place is beyond ±920mV, but it would be great if you could tell me if this is a countermeasure and if it is effective.

Best regards,

O.H