Hi Experts,

I am using LPM4.5 in my application and I am able to get proper LPM4.5 wakeup .

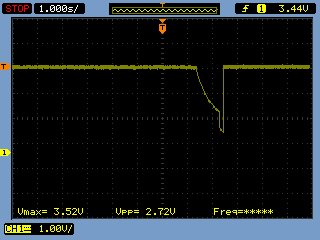

As per TI manual after wake-up from LPM4.5, the state of the I/Os are locked and remain unchanged until the application clears the LOCKLPM5 bit in the PM5CTL0 register. But the issue is when I clear this by PM5CTL0 &= ~LOCKLPM5; I am seeing a glitch for my one of the GPIO pin on the oscilloscope. The following image discribe this behavior.

Can you explain the reason behind this and solution to avoid this.?

Thanks In Advance.