Hello,

First of all let me explain that I have seen a few posts similar to this issue already. I still have some questions regarding what is happening in my system and the origins of the problem.

I am using the TM4C123BH6PZ in a single-master mode configuring to an ADC (MCP3428-E/ST) and the pull-up resistors on the bus are 4.99Kohms. The bus is running at 100KHz.

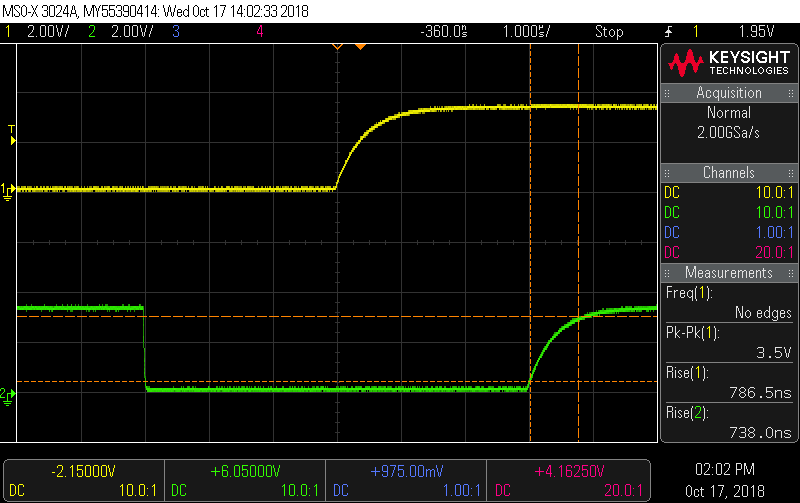

My issue is his: I observed a very short clock pulse that seemed to confuse the timing between the MCU and ADC, which caused the ADC to hold SDA low while waiting for the stop bit. See the captures below. Unfortunately I have only been able to capture this error with a logic analyzer. The measured pulse width of the runt pulse is .2599uS.

From reading about other users having similar problems with the tm4c, I am still not clear what the origin of the issue is. Does the tm4c glitch filter only handle inputs on SCL/SDA or is it possible for the glitch filter to also filter out these runt pulses on the output of SLC?

Is this a proven issue with the tm4c (and if so is there a diagnosis and solution?), or is it more likely something with my firmware or hardware? I did read one user claim that lowering the pull-up resistor values fixed the problem because the rise time of the runt pulse did not meet the specs, so the mcu was trying to re-establish correct communications. If this is happening in my system (since I have 4.99k instead of the conventional 4.7k pull-ups), why is the rise time not slow on all of the SCL pulses, instead of just a few random pulses?

Any ideas/tips are welcome, thanks!