Other Parts Discussed in Thread: MAX3232

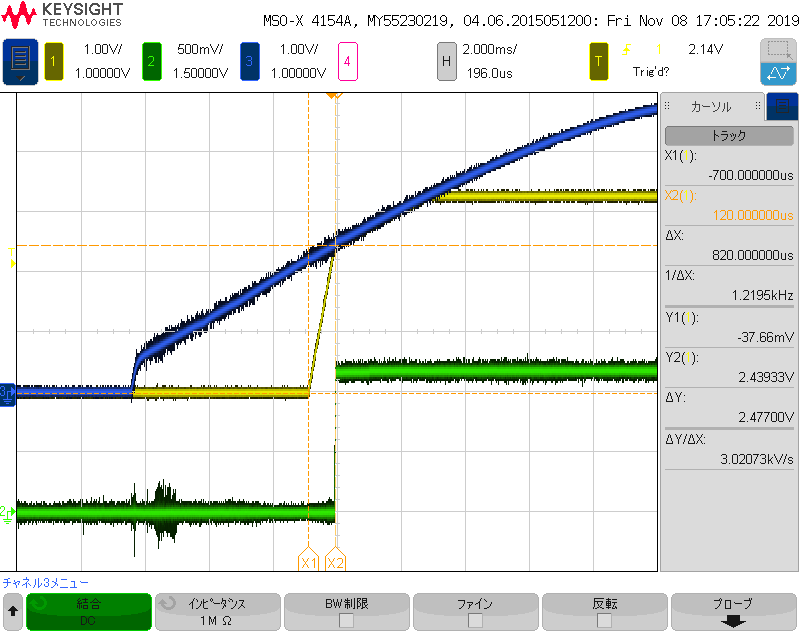

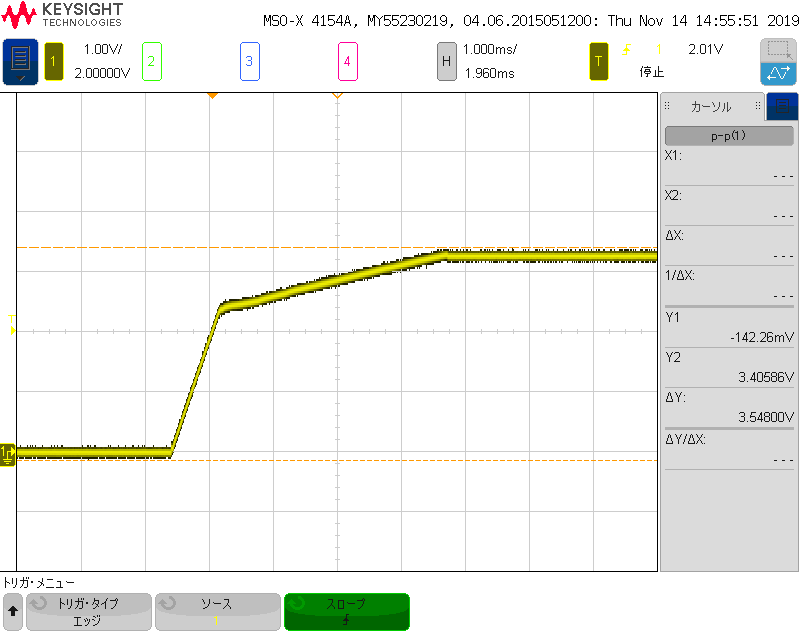

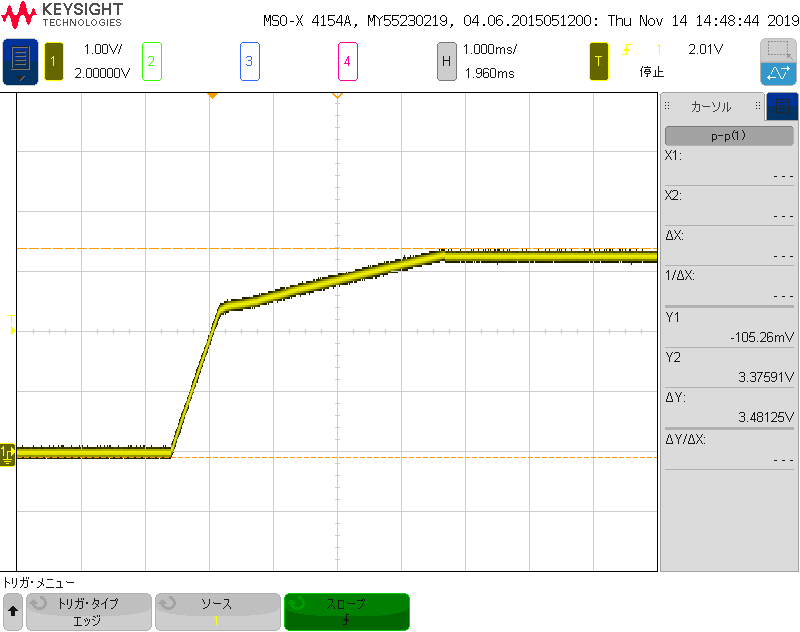

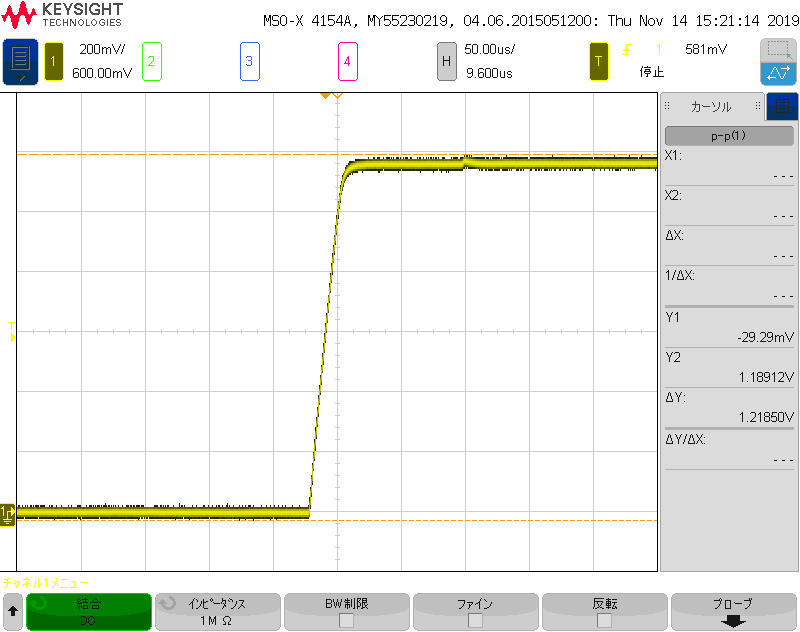

When VDD and VDDA are connected to the same power supply, VDDC begins to be generated when VDD reaches about 2.5V when the power is turned on.

If the rise rate of VDD is very slow, even when VDDC reaches 1.2V, VDD remains at about 2.5V.

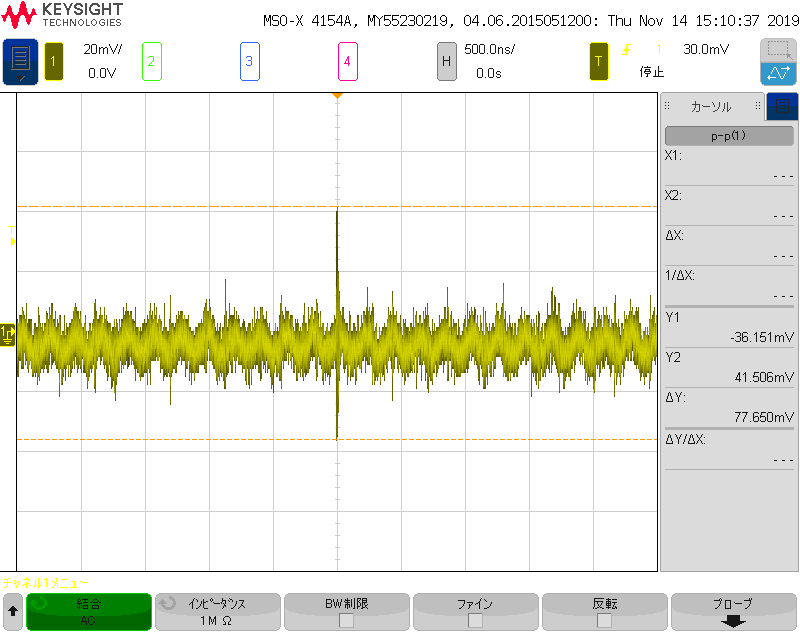

Is this situation not adversely affecting the internal power supply circuit?

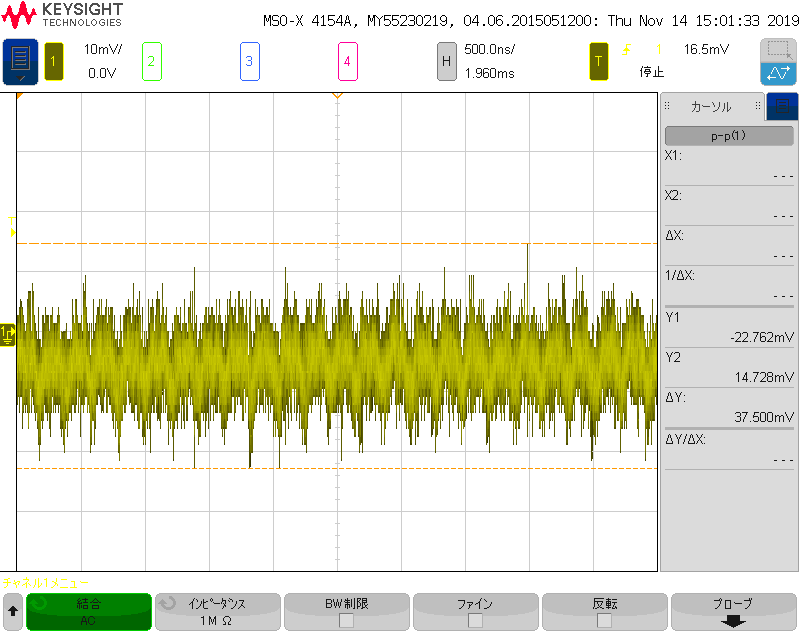

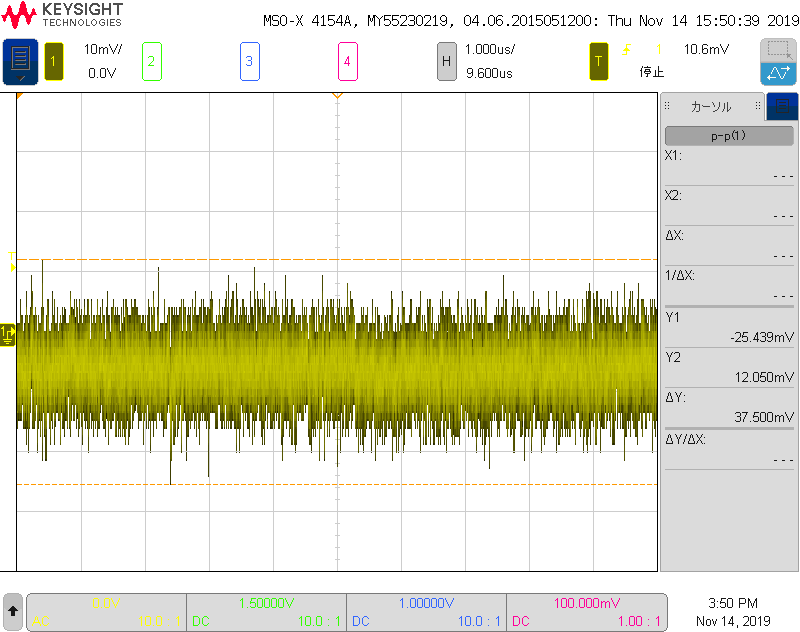

Although the mysterious burning of TM4C1299NCZAD continues, it is known that there is no problem with the external circuit.

I suspect that this situation is adversely affected.