Other Parts Discussed in Thread: EK-TM4C1294XL,

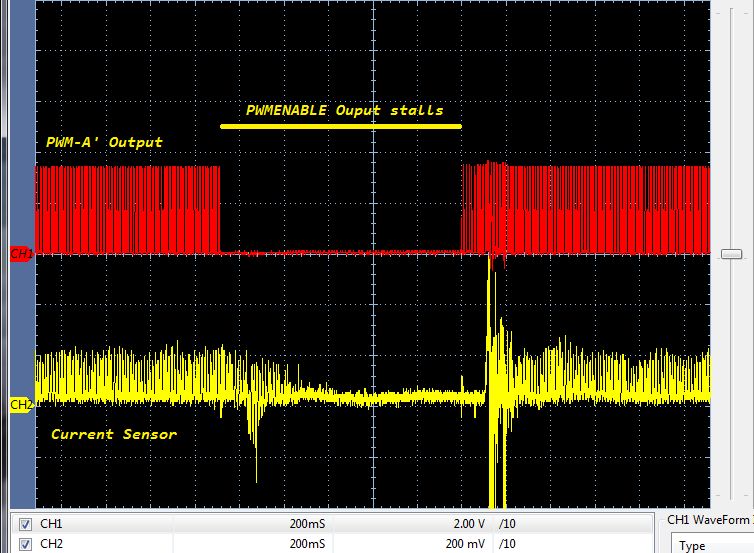

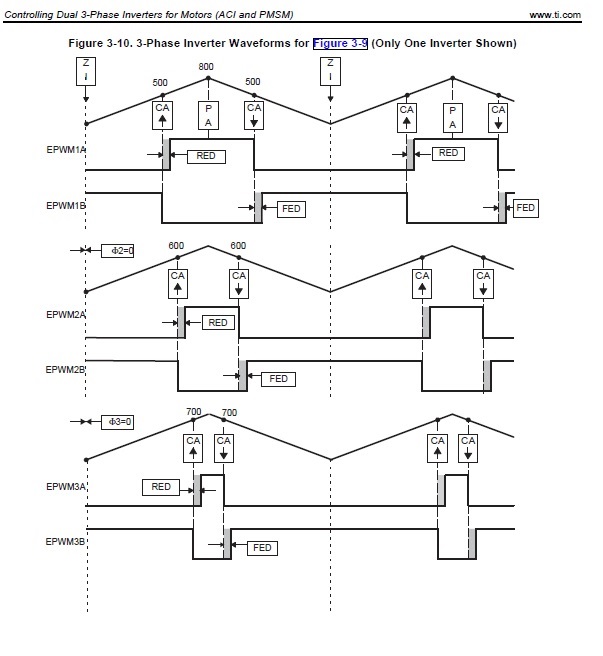

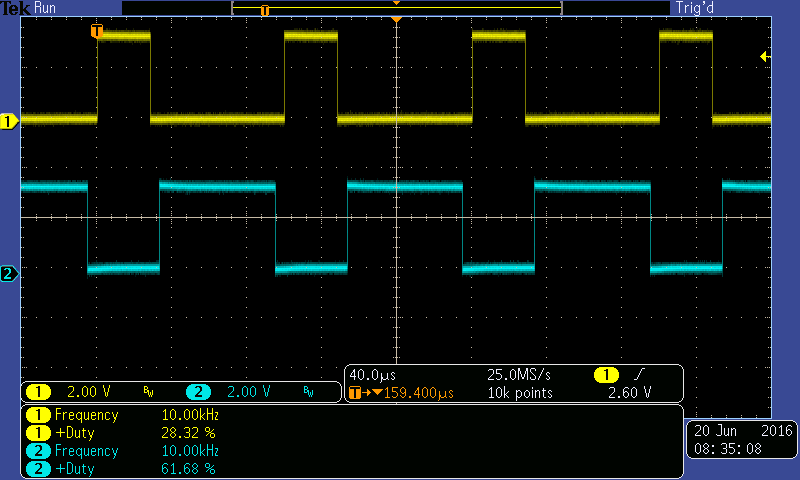

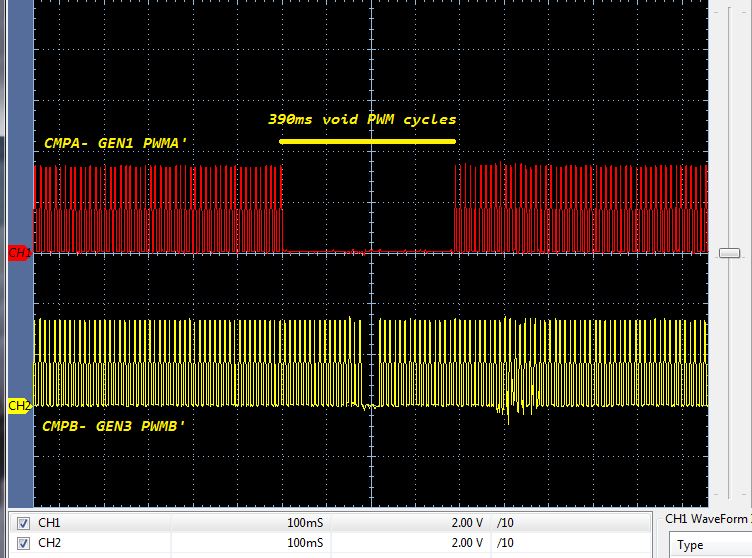

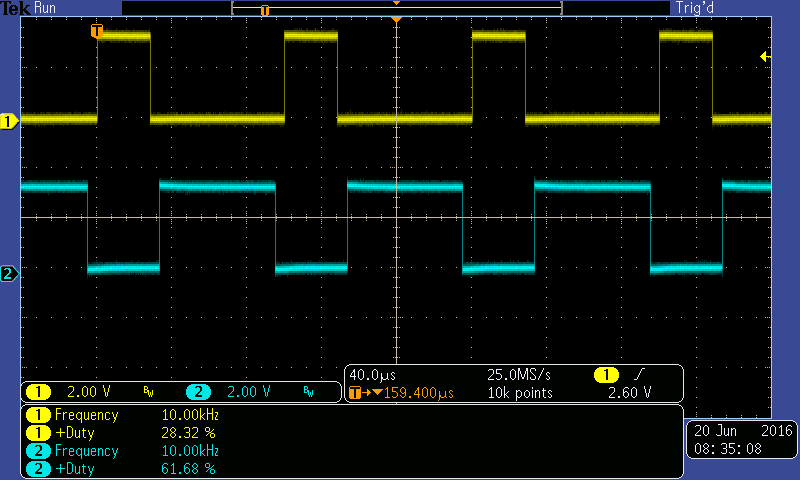

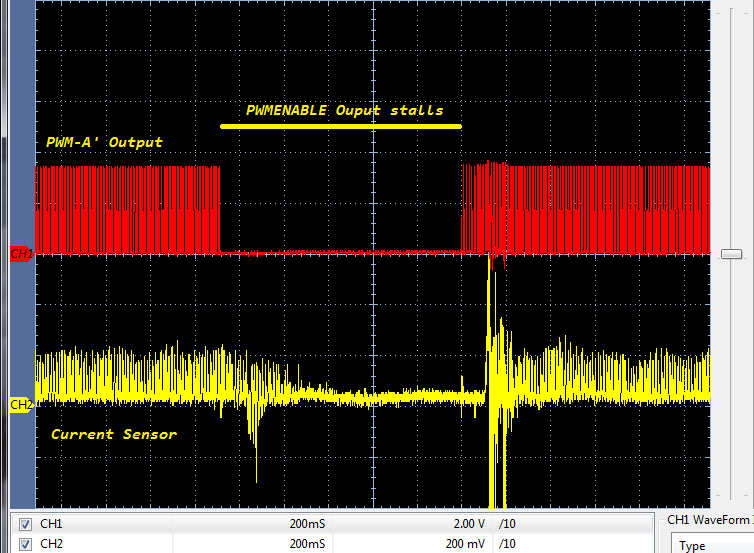

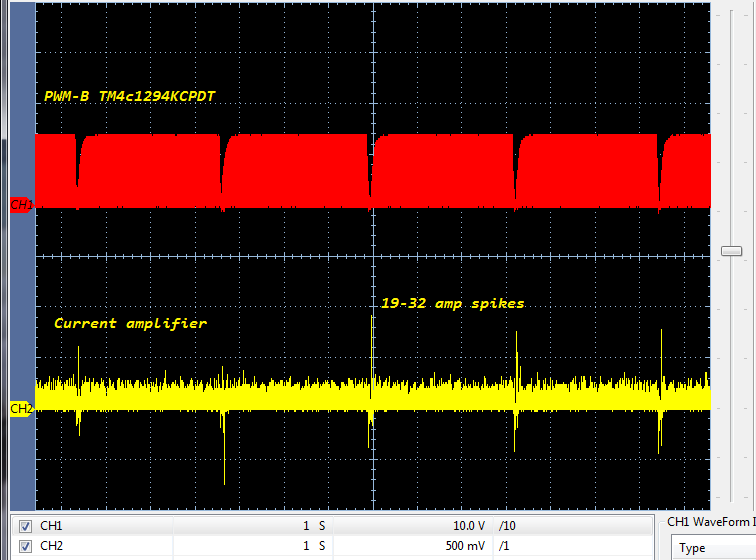

Have past posted similar question as to what can cause a reoccurring electrical disturbance on PWM between 1-5 seconds apart. Yet the 1/2 bridge output drives are very clean most of the time than suddenly 100-200ms crash of all PWM periods. How could I be so blind not to see this electrical storm as anything but disastrous.

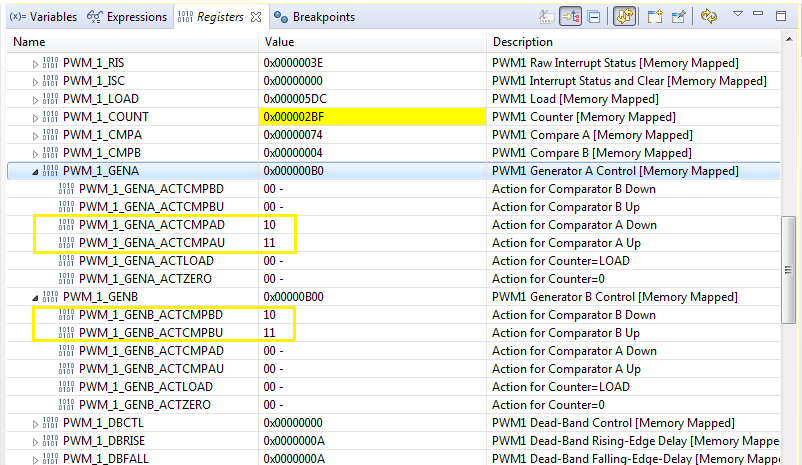

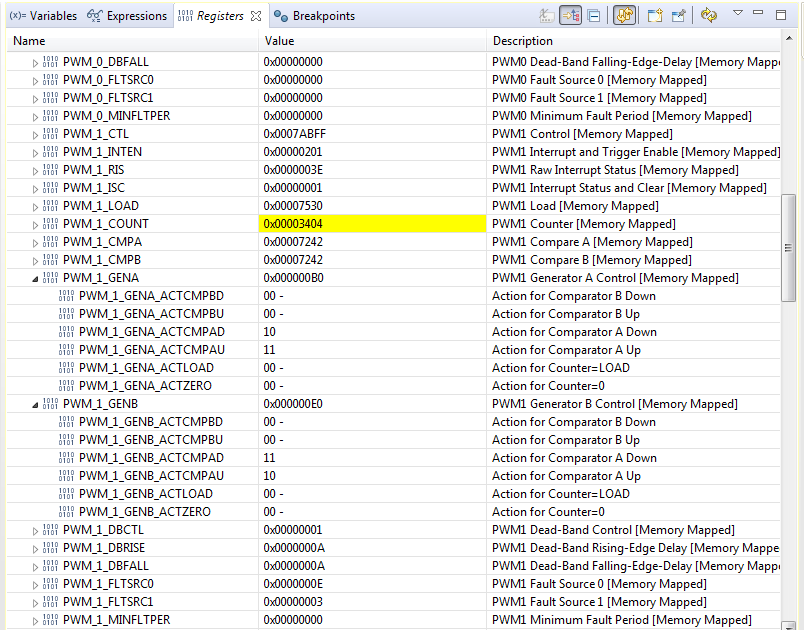

It has more recently occurred to me that global synchronous updates may be out of sync during GPTM driven output intervals PWMENABLE register. Hence PWM outputs being enabled during generator counts being loaded may not be the best of all conditions. Oddly this frequent random storm does not crash the DC inverter but absolutely reeks havoc on hardware from the EMF spike/s that occur. Sort of like mowing your lawn where grass deepens having to push even harder to get through the rough. Upon exit there is a sudden moment when you accelerate then even out the self propelled speed. Since then purchased 42" deck rider mower but that's another yard story.

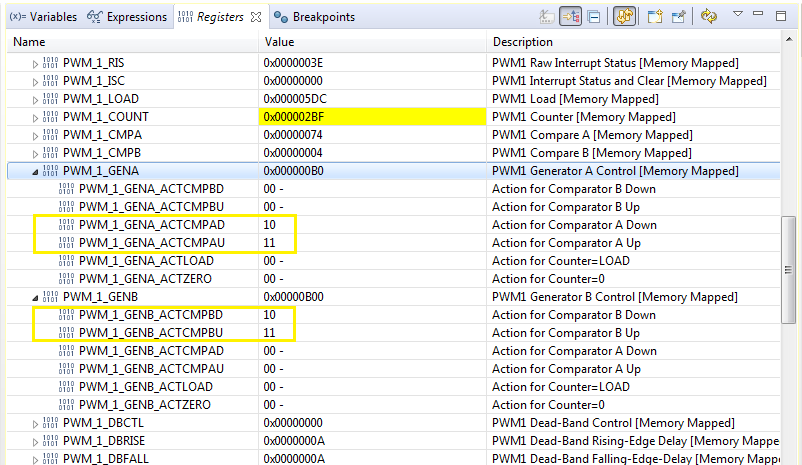

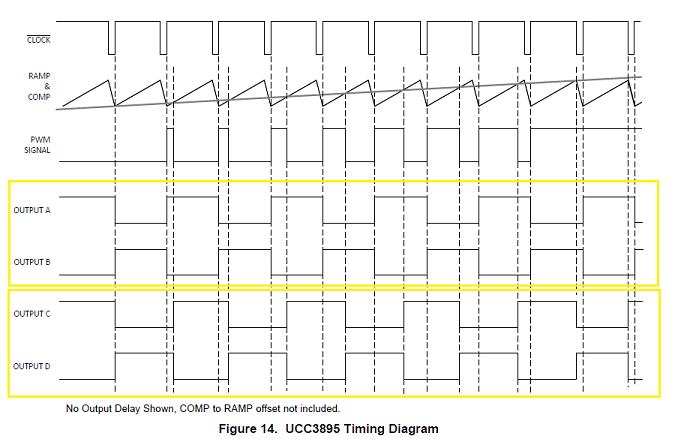

Anyway the GPTM configured OSHT has an interrupt handler function to control PWMENABLE and OSHT count is reloaded between 2 PWM periods inside the ADC interrupt handler.

Then there is another GPTM to capture edge times for the ADC interrupt, used to determine a new PWM edge for driving commutation via PWMENABLE, another NVIC interrupt.

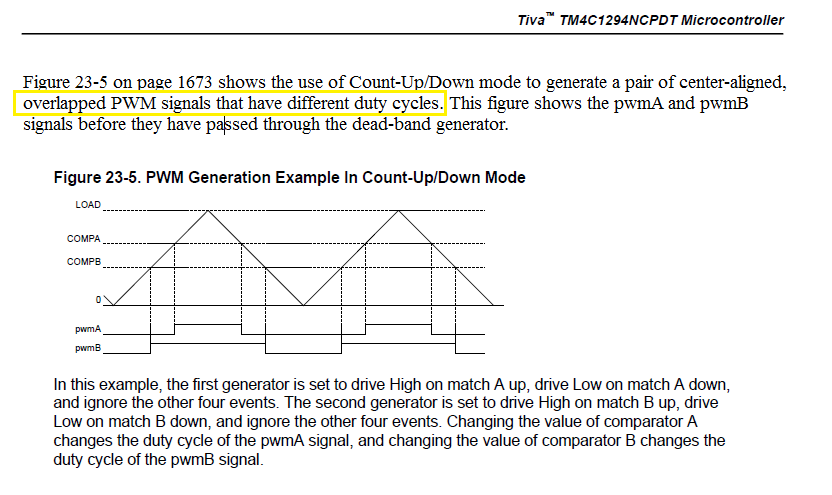

Perhaps PWM (over run) occurs during global synchronous updates, ADC interrupts indirectly control the outer commutation function loop via OSHT timeout.

The question is how to stop over run without adding to much complexity and or disrupting PWM commutation cycles?

My first guess being to add a while Not loop into OSHT handler that drives commutation events, is that to evasive?

Has anyone ever seen this same random PWM electrical storm?