Other Parts Discussed in Thread: ADS8326, ADS8319

Tool/software: Code Composer Studio

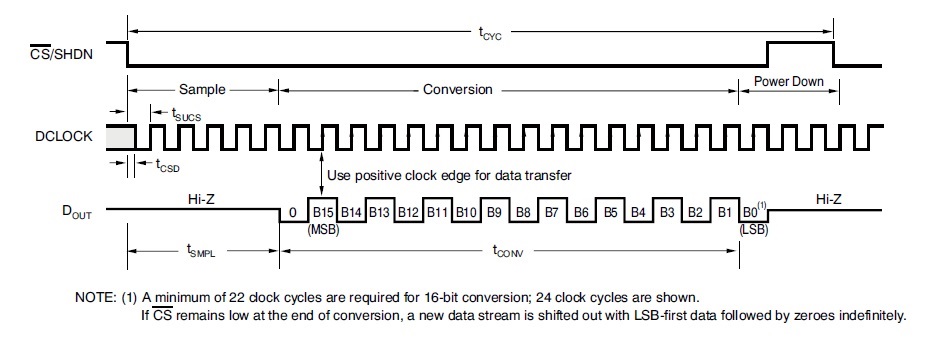

I have a question about SPI timing. I would like to read a 16 bit ADC (ADS8326) at 250 ksps using a TM4C123 microcontroller running at 80 MHz. The timing diagram for the ADC is attached.

I need to drive CS low and have the MISO pin ignore 5 clock cycles before collecting data (attached timing diagram). To do this, I think I need to set up the clock and CS pins as pwm signals and trigger the SSIDataGet command off of the CS timer. My question; how do I set it up to read at the correct time? I would like to set a flag in the ISR that is recognized in the main while(1) loop. Do I need to introduce a delay, as in the text below, or will the MISO wait for the ADC output to drive the pin LOW?

if(readFlag == true){

SysCtlDelay(readDelay);

SSIDataGet(SSI0_BASE, &dataPoint);

}

Thanks for your help.