Hi TI team

Could you help me to get the IEC60730 lib for MSP432 serial chips? I only find the one for MSP430.

similar as this one, www.ti.com/.../MSP430-IEC60730-SW-PACKAGE

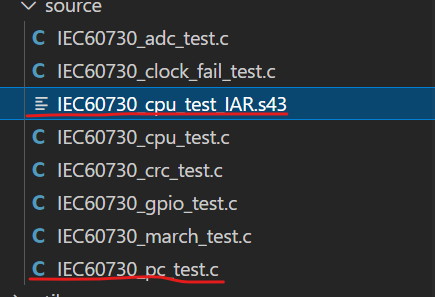

If TI doesn't have the lib for MSP432, could you help to share us some related document to achieve the below function, thanks

Regards,

Neo