I've implemented the UART Interrupts on my TM4C using TivaWare functions.

The program is simple:

- an interrupt is triggered when data is received on the UART

- Each character received is echoed back between curly brackets

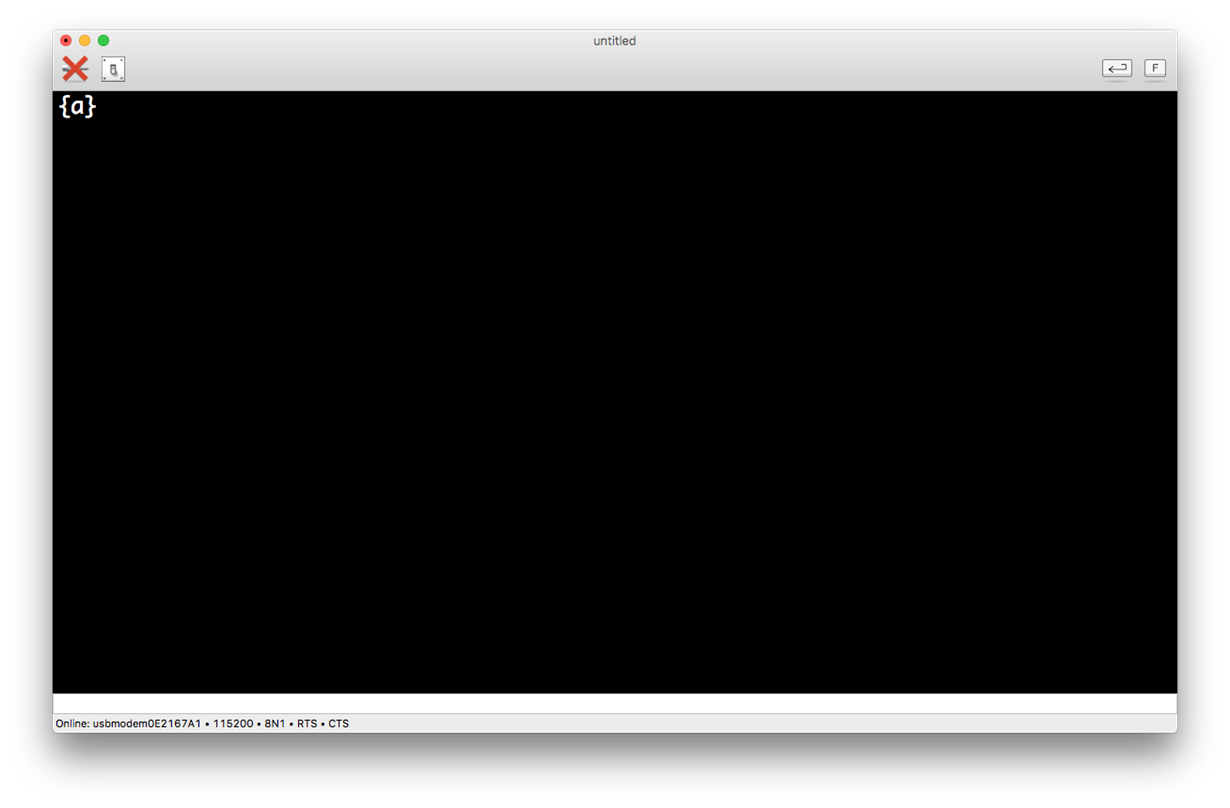

So if I were to send 'a' from my computer, I would get back '{a}'. Example:

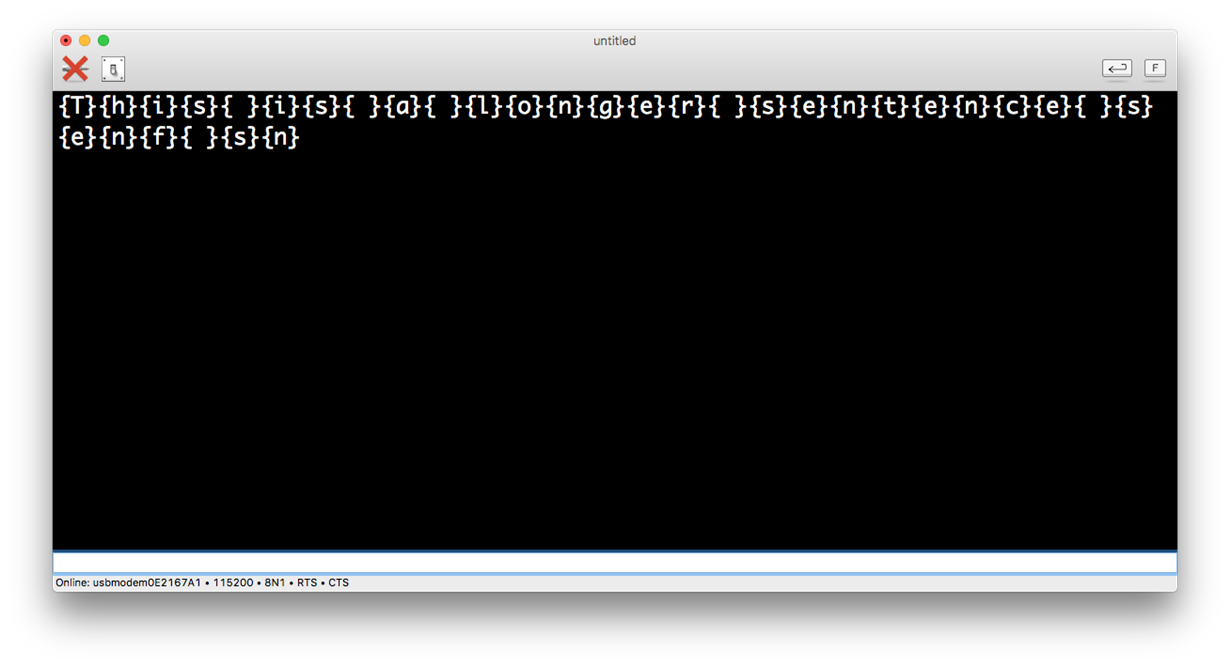

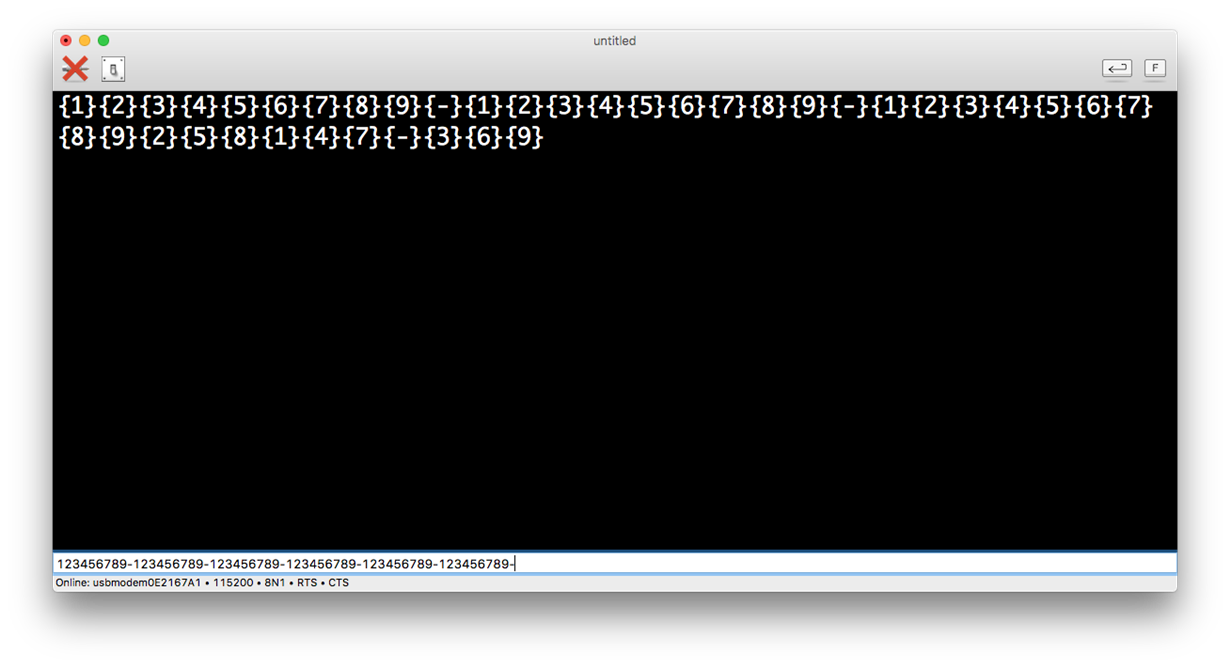

The problem is when I test sending longer messages at once: the first few charaters are echoed back, then at one point there are missing characters:

EXAMPLES

Note that the messages in these example were written in full in the text field below and sent at once by pressing Enter. I'm doing this to simulate programmatically sending data over serial, which should happen as fast.

In this example, I sent the sentence 'This is a longer sentence sent for testing' :

In this example, I sent '123456789-123456789-123456789-123456789-123456789-123456789-'

Details:

- Hardware: Using a Tiva TM4C launchpad

- Using UART 0, on pins PA0 and PA1

- Baud rate : 115200, no parity, 1 stop bit, 8 bit words

The Code:

#include <stdint.h>

#include <stdbool.h>

#include "inc/hw_memmap.h"

#include "inc/hw_types.h"

#include "driverlib/gpio.h"

#include "driverlib/pin_map.h"

#include "driverlib/sysctl.h"

#include "driverlib/uart.h"

#include "inc/hw_ints.h"

#include "driverlib/interrupt.h"

void setup(void);

int main(void) {

//

// Setup

//

setup();

while(1) {

}

}

//****************************************************************************

//

// UART CODE

//

void UART0_IntHandler(void) {

//

// UART Interrupt Status

//

uint32_t ui32Status;

//

// Get interrupt status

//

ui32Status = UARTIntStatus(UART0_BASE, true);

//

// Clear interrupt flag

//

UARTIntClear(UART0_BASE, ui32Status);

//

// loop while there are chars

//

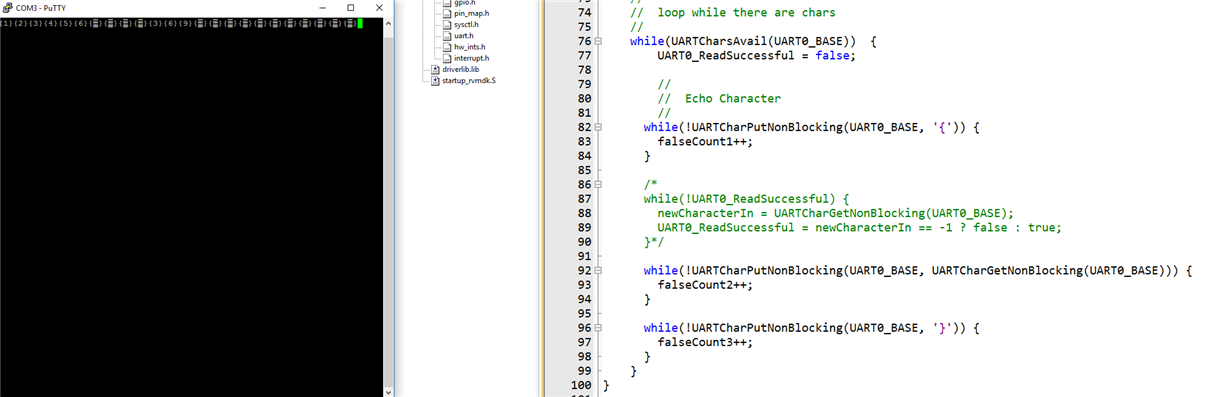

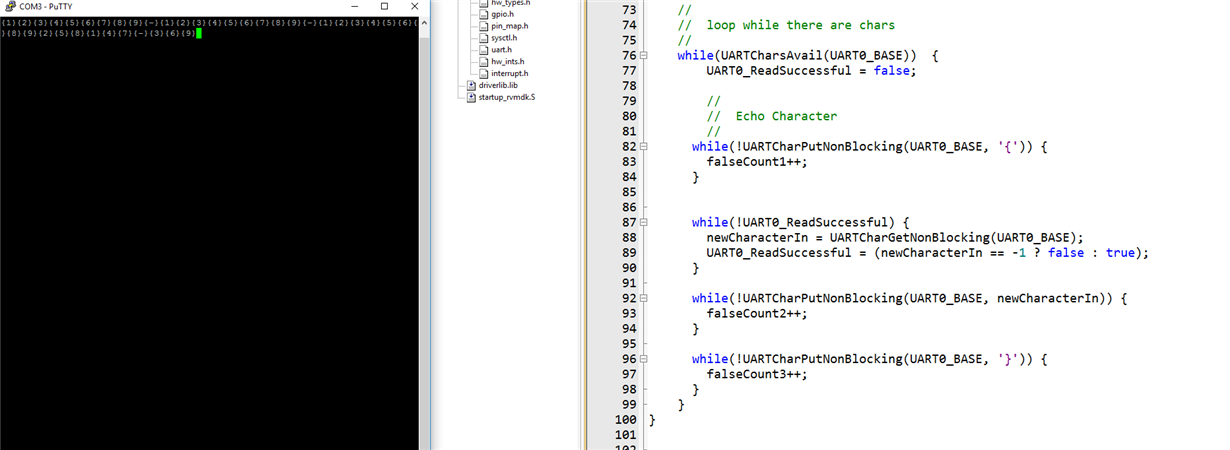

while(UARTCharsAvail(UART0_BASE)) {

//

// Echo Character

//

UARTCharPutNonBlocking(UART0_BASE, '{');

UARTCharPutNonBlocking(UART0_BASE, UARTCharGetNonBlocking(UART0_BASE));

UARTCharPutNonBlocking(UART0_BASE, '}');

}

}

//****************************************************************************

//

// SYSTEM SETUP CODE

//

//

// UART Setup function

//

void UARTSetup(void) {

//****************************************

//

// UART0 SETUP

//

//

// Enable the clock on UART 0 and GPIO A

// (UART 0 is on pins PA0 and PA1)

//

SysCtlPeripheralEnable(SYSCTL_PERIPH_GPIOA);

SysCtlPeripheralEnable(SYSCTL_PERIPH_UART0);

//

// Wait for the UART0 module to be ready.

//

while(!SysCtlPeripheralReady(SYSCTL_PERIPH_UART0))

{

}

//

// Configure pins PA0 and PA1 for UART

//

GPIOPinConfigure(GPIO_PA0_U0RX);

GPIOPinConfigure(GPIO_PA1_U0TX);

GPIOPinTypeUART(GPIO_PORTA_BASE, GPIO_PIN_0|GPIO_PIN_1);

//

// Configure UART Settings:

// UART: 0

// Baud rate: 115200

// Word length: 8

// Stop bits: 1

// Parity: None

//

UARTConfigSetExpClk(UART0_BASE, SysCtlClockGet(), 115200, UART_CONFIG_WLEN_8|UART_CONFIG_STOP_ONE|UART_CONFIG_PAR_NONE);

//****************************************

//

// UART0 INTERRUPT CODE

//

//

// Enable UART0 Interrupts

//

IntEnable(INT_UART0);

//

// Select UART0 Interrupts

//

UARTIntEnable(UART0_BASE, UART_INT_RX | UART_INT_RT);

}

//

// System setup

//

void setup(void) {

//

// UART Setup function

//

UARTSetup();

//

// Enable Processor Interrupts

//

IntMasterEnable();

}