Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

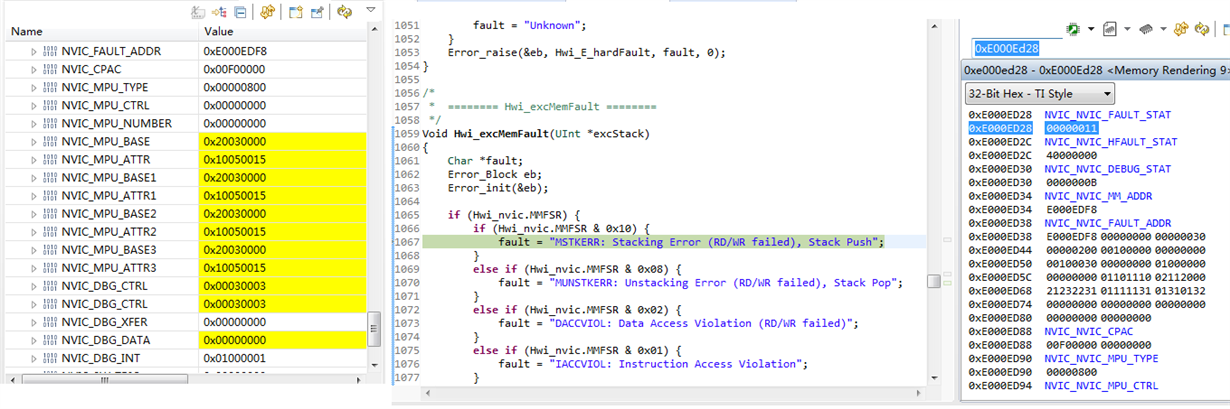

If I suspect that in my app some code modifies a specific RAM address (or some address randomly within a range), can I use MPU to debug this? My idea is:

- Place a useless array to cover the address range.

- Setup MPU for this area. I think I can use "module ti.sysbios.family.arm.MPU" or TivaC MPU device driver. The problem is: when a violation occurs, can I know the PC that trigger the violation? By default without enabling the MPU interrupt, a hard fault exception will happen.

- How to enable the interrupt for MPU (MPUIntRegister in driverlib can't be used in RTOS project, and there is no function to deal with interrupt in "module ti.sysbios.family.arm.MPU")? Can I get more information about the error in the interrupt function?

Thanks