Please let us know charge pump block power up timing.

If wake and EN_GATE are low,is Charge pump block powered up regardless of the status of wake and EN_GATE ?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Please let us know charge pump block power up timing.

If wake and EN_GATE are low,is Charge pump block powered up regardless of the status of wake and EN_GATE ?

Hi Kura,

We can run a wake-up test today of PVDD, VCPH, WAKE, and EN_GATE to capture high-side charge pump timing on powerup.

I'll let you know of the results later.

Thank you,

Aaron

Hi Kura,

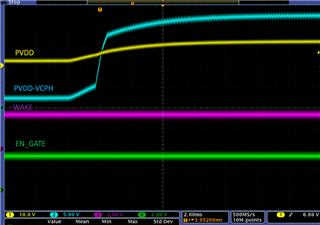

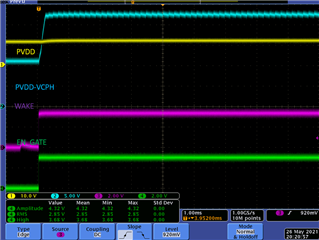

I took two waveform captures of PVDD, PVDD-VCPH, WAKE, and EN_GATE for two different scenarios. For these tests I used the DRV8305-Q1 EVM.

First waveform is triggered upon PVDD powerup at 12V.

Second waveform is triggered on WAKE rising edge when PVDD is already powered up.

Let us know if would like us to capture any more waveforms tomorrow.

Thank you,

Aaron

Hi Kura-san,

The charge pump is inactive due to the status of the WAKE pin. When WAKE is low, the DRV8305-Q1 is in SLEEP mode which disables internal logic, including logic for charge pump control. When WAKE > 3V, then the device will exit from SLEEP mode and enable the internal logic used to power up the charge pump.

Thanks,

Aaron

Aaron-san

Thank you for your reply.

Please let us know more about first waveform.

1.If EN_GATE and WAKE are GND,and then PVDD is poweed up, does PVDD-VCPH start up ?

This waveform shows that EN_GATE,WAKE are 3.3V level before PVDD powerup..

2.In this case internal logic of DRV8305NQPHPRQ1 is already active ?

3.Please let us know about connection information at your test.

Hi Kura-san,

1. If WAKE = GND and EN_GATE = GND, then PVDD is powered up, PVDD-VCPH should NOT start up because the DRV8305-Q1 will be in a sleep state and the charge pump will be disabled until WAKE goes high (second waveform)

2. The internal logic of DRV8305NQPHPRQ1 is active once PVDD is higher than the PVDD_UVLO threshold (4.7V).

3. I used the DRV8305-Q1 EVM for these tests. Waveform 1 was captured by plugging in the micro-USB cable then powering PVDD = 12V. Waveform 2 was captured by powering PVDD = 12V and then plugging in the micro-USB cable. (plugging in the micro-USB cable initializes the MCU, which sets WAKE and EN_GATE high).

Thanks,

Aaron