Other Parts Discussed in Thread: DRV8353,

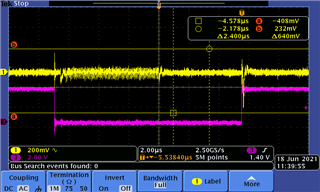

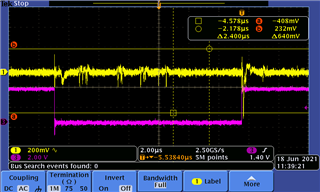

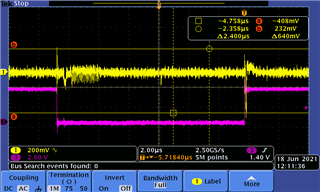

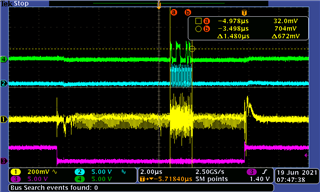

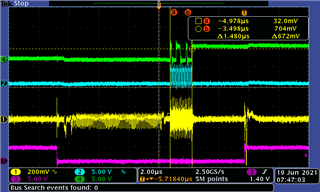

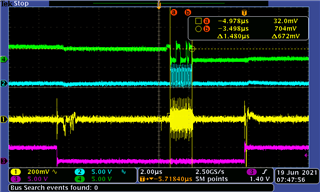

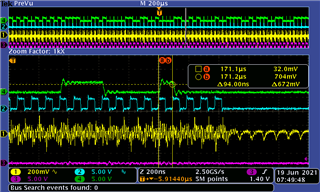

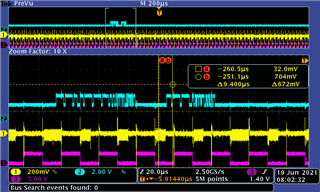

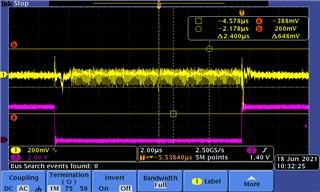

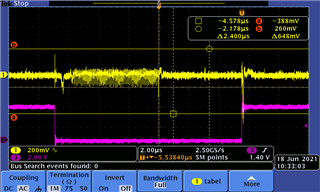

With all the layout changes suggested before, I have the exact same current sense problem as I had in the previous iteration. Here are snapshots of the current sense line AC coupled along with the gate drive signal.

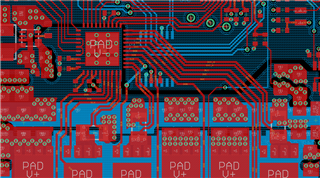

No real changes from the last time. Occasionally one or more channels have noise for the entire duration, and sometimes only to the halfway point. My layout looks like the following (which is basically the same as the one I posted at the end of the last thread):

I'm not too surprised that the layout problems didn't fix anything, as the same basic layout did not exhibit this problem with the DRV8323RS based design I previously had. No doubt this is better, but whatever the problem is, it did not resolve it.

Any other ideas?