Other Parts Discussed in Thread: CSD19532Q5B

In a motor drive application a DRV8350RH smart gate driver is used to control the CSD19532Q5B MOSFET transistors of a three-phase inverter.

The driver works in 3PWM mode, the IDRIVE resistor is set to have 150mA/300mA (source/sink ) current. The VM is supplied by the help of the internal BUCK regulator. The passive components are selected based on the datasheet.

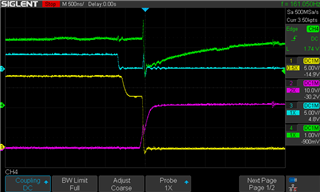

During the testing we met with the following issue, when PWM GHx goes from high to low. When INHx is pulled down, it's corresponding GHx doesn't immediately go down (see scope figure). Instead, it does so in two steps. In the first step the GHx is weakly brought down for about 400ns (not enough to switch off the MOSFET) and then after the signal is fully brought down. This only happens to GHx not GLx and causes a brief short circuit and brief error signal.

(Blue: INHx, Yellow: GHx. Purple: GLx, Green: FAULT_N, measurement was done without motor, having zero current)

We increased/decreased the IDRIVE resistor, but the curves are the same, only the rate of signal rise or fall changes.

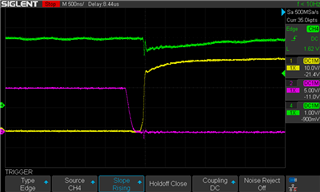

In the opposite case, when GHx goes low to high works properly as it is indicated on the figure below (the only issue is that the deadtime seems to me 500ns instead of the 100ns mentioned in the datasheet)

Could you suggest some solution to solve the issue during turn-off of the upper transistor?

Thanks in advance