Other Parts Discussed in Thread: DRV8801A-Q1, DRV8801, DRV8844, DRV8873

We have designed a multi-channel solenoid valve driver with the DRV8873H-Q1.

This operates from 14.4V nominal supply and uses PWM of one or the other output (with the other output held at supply) to produce load currents varying from 1A in the OUT1-2 direction to 1A in the OUT2-1 direction depending on a signal input. In our design open load test/detection is disabled, current regulation and trip are enabled, and we have tried 13V/us, 18.3V/us and 34V/us slew rates.

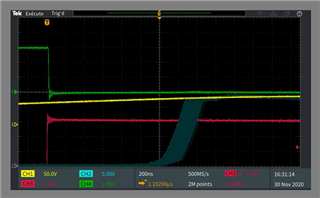

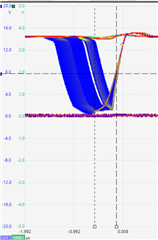

We found that the PWM outputs in our design exhibit jitter which becomes more significant as the pulse widths reduce, for example at 96 or 97% duty cycle we see:

This shows significant jitter giving rise almost to two discrete pulse widths.

I have searched this forum and other places for references to jitter and tried the small number of fixes all to no avail.

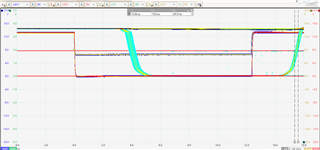

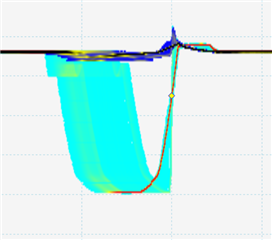

We bought the DRV8873HEVM to try out the reference design and we were surprised to see that this behaves in an identical manner:

There are differences to our design (20kHz PWM on EVM cf. 10kHz on our design) but nothing significant.

Is this output jitter a 'feature' of the DRV8873H device?