Hello, I am a TI FAE, we want to know if the MOSFET and half bridge circuit may cause permanent damage to the internal drive circuit and charge pump of DRV8353 when DRV8353 works at high current. If so, what is the damage mechanism?

Here are the details:

This problem is based on links

e2e.ti.com/.../3694693 tisearch=e2e-sitesearch&keymatch=DRV8353#3694693

In the last consultation, we did not solve the problem of two-phase protection of the system under high current.

However, at present, we are temporarily focusing on solving the problem of DRV8353 triggering protection when working with high current. The main purpose of this post is to know the specific triggering reason of protection.

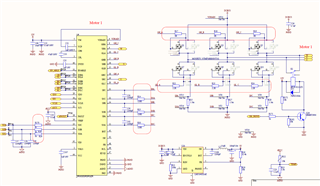

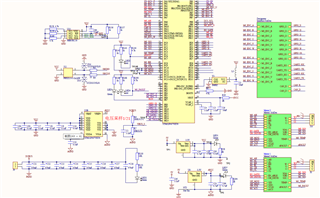

The circuit diagram is shown below. Now we pay more attention to the threat to the charge pump and drive circuit of DRV8353 when the half bridge composed of MOSFET flows through high current.

At present, we have made the following attempts:

When we keep the detection and protcetion about GH_ A/GL_A and SPN/SNA , the current increases due to artificial loading on the motor. When the motor current reaches 60-70A, DRV8353 triggers some protection, but SPI cannot work at this time, so it is impossible to know what protection is triggered.

However, in my opinion, this does not trigger the overcurrent protection, because the OCP is set at 200A in this case, and the DRV8353 does not trigger the protection immediately when the current reaches 60-70A, but only after a few seconds. So we began to explore what kind of protection DRV8353 triggered.

So we close GH_ A/GL_ A and SPA/SNA detect and protect the motor at the same time. The first problem is that the over temperature protection is triggered. It should be noted that the over temperature object here is not DRV8353, but MOS tube. This is caused by the temperature rise of MOS tube. MCU detects that the temperature of MOS tube is too high, so it turns off DRV8353.

We turned off the over-temperature protection and continued the same experiment. Under similar working conditions, the power supply triggered the over-current protection. However, this power supply will trigger protection only when there is serious overcurrent, which indicates that there may be a problem that makes the instantaneous value of current very large.

However, different from the previous situation, when we restart the system, we find that GDUV fault occurs, which is known by checking the register of DRV8353. No matter how to restart or reset, this problem cannot be eliminated. We believe that in the last experiment, some processes of the power circuit led to the permanent damage of the charge pump or drive circuit in the DRV8353.

It should be noted that all the above experiments are not triggered immediately when the current reaches 60-70A, but after repeated locked rotor for several times, which is a process that needs to be accumulated. In other advisory posts on DRV8353, GDUV abnormalities also occur to many engineers under high current or high Vdrain, so I think this is a common application problem.

I also hope you can try to give some possible wrong directions and solutions, thank you!