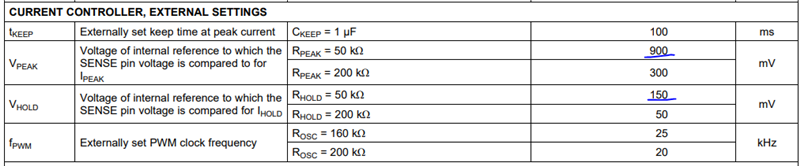

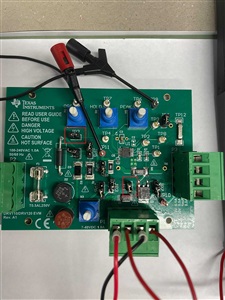

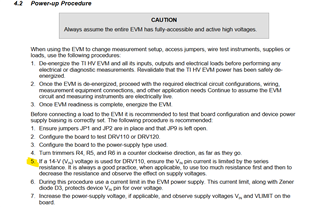

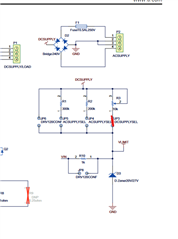

I have designed a custom board on DRV110 to control solenoids of different hold and peak currents, settable by pots on board. The board is supplied with a voltage of 24V which is also the supply voltage for solenoid. The IC is powered by 15V generated from on board DC DC converter.

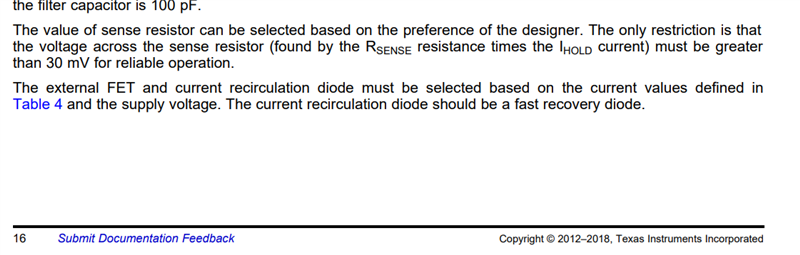

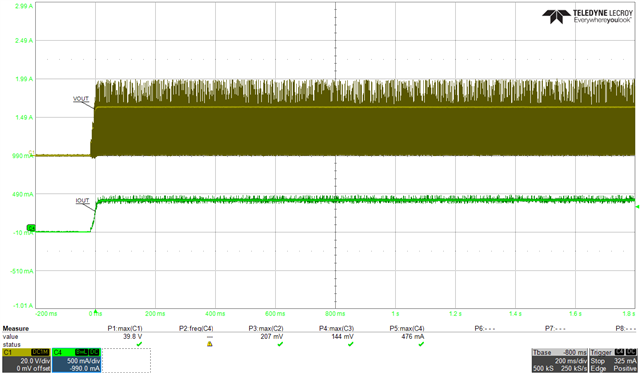

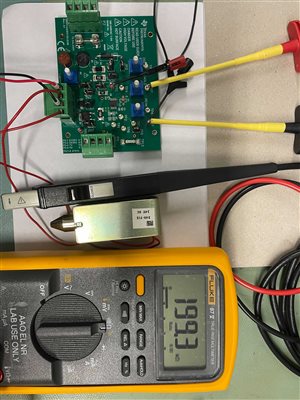

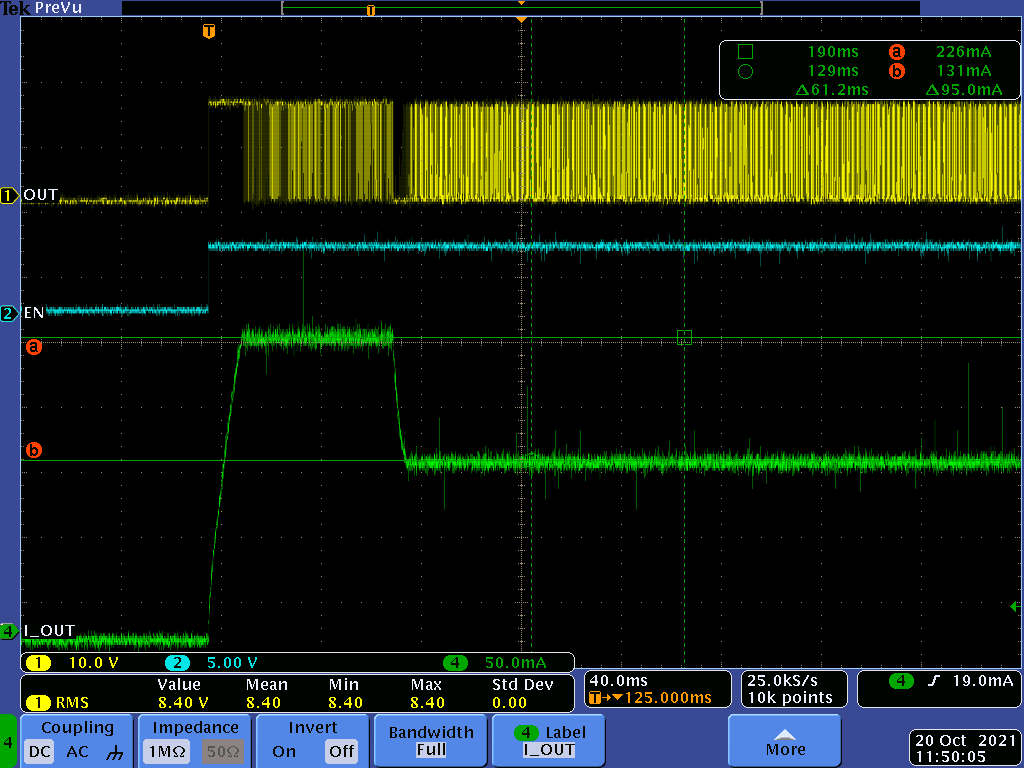

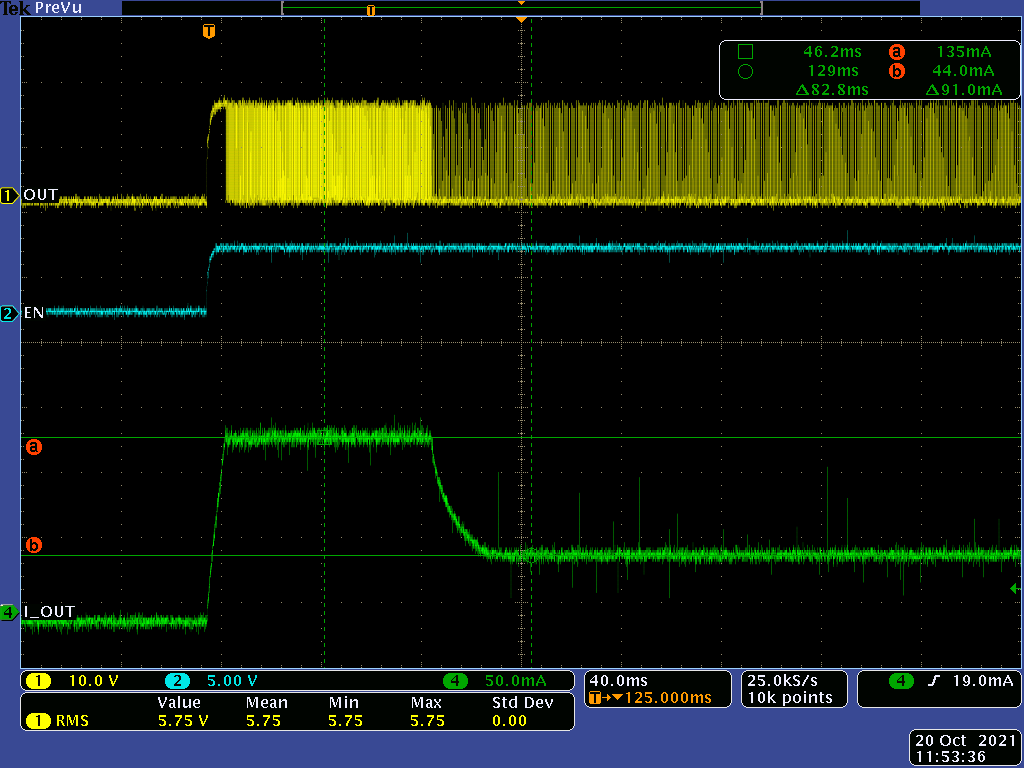

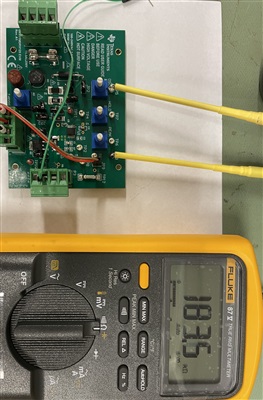

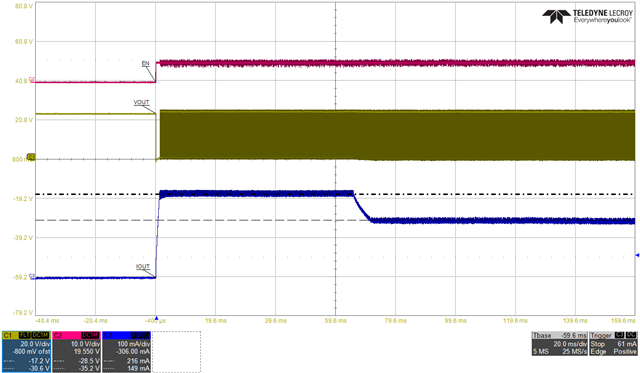

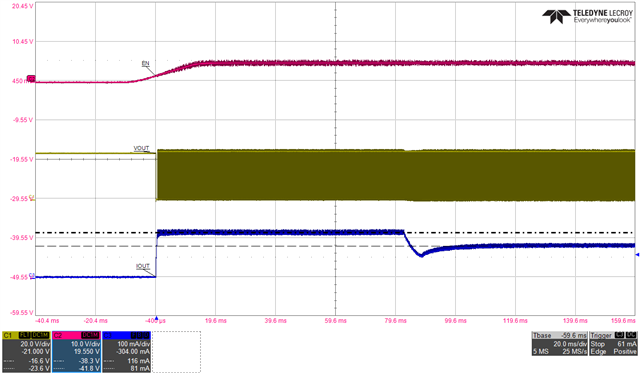

I am trying to set peak current of 0.48A and hold current of .35A. The sense resistor value is 0.2 Ohm. The calculated Rpeak and Rhold are 625kOhms and 142kOhms respectively which is set by the pots. However the current is not as expected, the OUT signal which drives the FET gate is high all the time and current remains constant ( limited by R of solenoid) irrespective of value set by pots.

I do not understand what am I missing here. I have checked the resistance on driver pins and they seem to be correct. The voltage on hold and peak pin of driver is 1V which is different from datasheet's value for similar values of hold and peak resistance. The drop across sense resistors is more than 30mV for these set values.

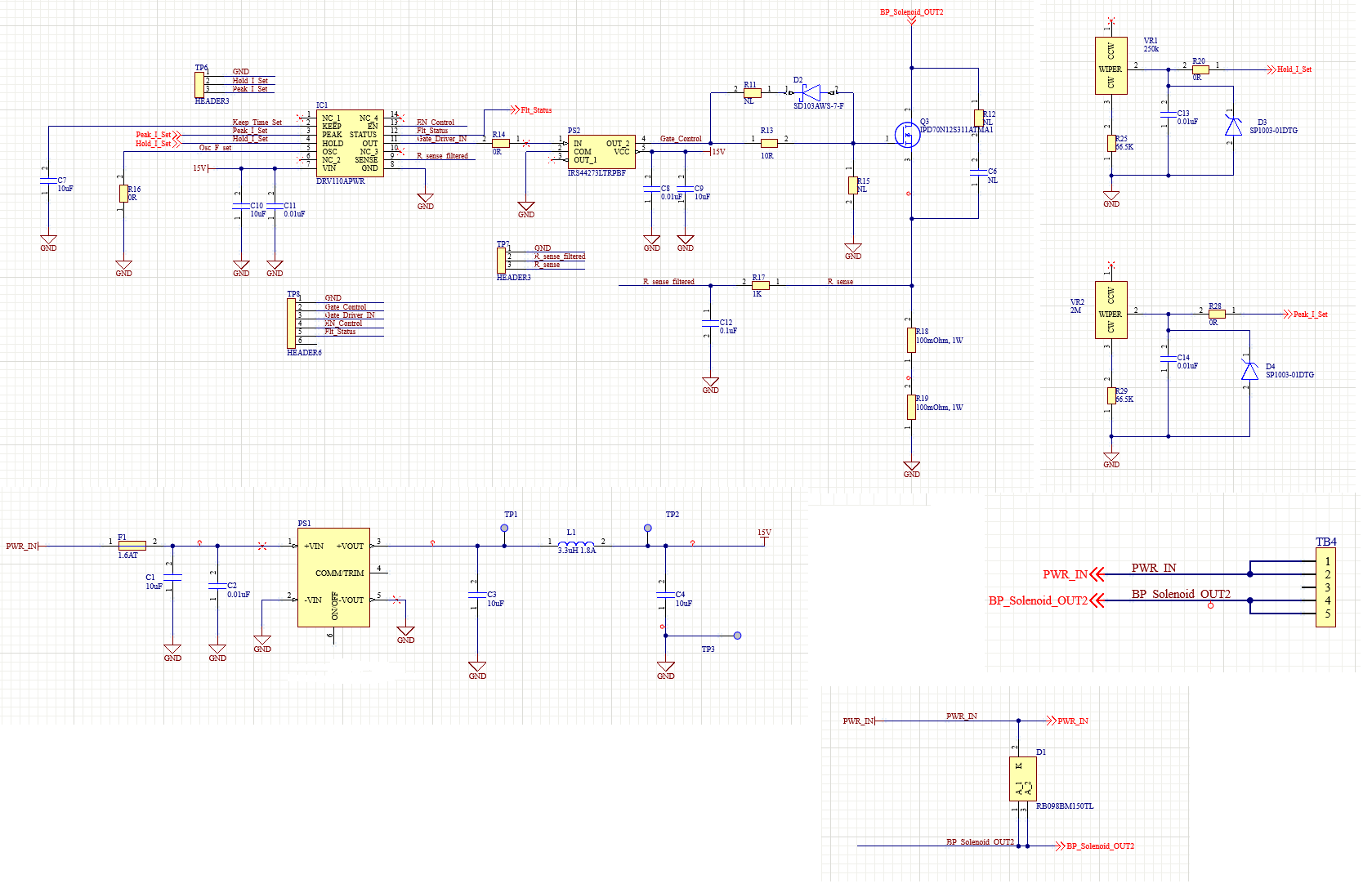

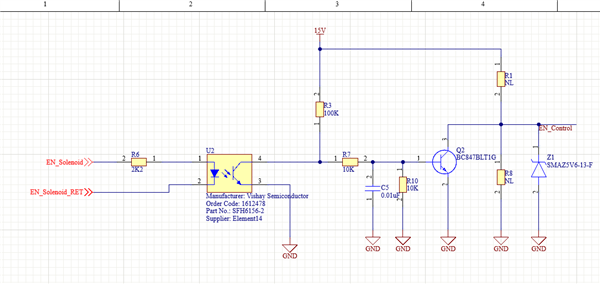

Attached relevant sections of schematics.