Other Parts Discussed in Thread: DRV8316

Hello,

I have been evaluating this eval extensively for the past week and I have a few questions.

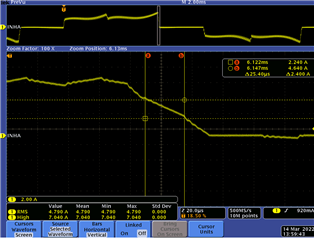

1) About the slew rate setting, the observed slew rates are quite different from the slew rate setting that is set. I see that only typical values are stated in the datasheet, so I am guessing there is quite a variation on how SR is achieved in the DRV8316. How much of this error is the DRV8316? Is this error vastly different between different DRV8316 batches or are they more or less deterministic? Is this motor dependent as well? We just want to isolate the fact that variation in this feature doesn't drastically affect motor performance. For reference here were the measured slew rates vs the set slew rates I have observed:

25V/us: 44.4V/us

50V/us: 46.2V/us

125V/us: 214.3V/us

200V/us: 342.9V/us

2) About active demagnetization, how do I go about testing/verifying that it is making a difference?

3) I am kind of confused by how cycle by cycle current limiting is implemented. Section 8.3.11 of the datasheet says that VREF is used for I/V converter as reference, but in 8.3.13, it says that AVDD is used as reference? If the former is true, how does current limiting work when the SOx output is dependent on the voltage at VREF/ILIM pin, which is compared to the VILIM set by that very same pin?