Hello,

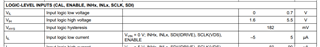

The datasheet of DRV8343SPHPRQ1 states there exists an input logic hysteresis of 182mV (typ) for the SCLK pin.

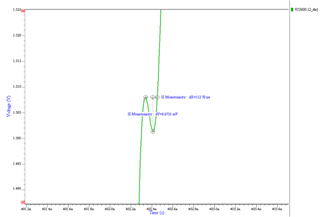

We would like to confirm in such a case whether the following non-monotonicity in the SCLK waveform would be of no concern for the SCLK normal operation.

The said non-monotonicity exists for 6.673mV and for a time period of 112.7ps. We expect this waveform distortion will be rejected by the input hysteresis ( as 6.673mV < 182mV) which will prevent a false switching.

Please confirm.

Also please let us know if there exists a minimum specification for the input hysteresis.