Hi,

This thread is related to previous one:

Aaron Barerra is the TI Engineer most familiar with this design.

I replaced the BSO150N03MDG FETs with the AUIRFN8459TR. Same pin-out, dual FET pkg. The dimensions are slightly larger, but I could solder them right in where the previous FETs were.

The motor tries to turn in InstaSpin Lab 01b, but just fitfully moves a small fraction of a revolution. Here's a comparison of relevant characteristics:

| FET | Vgs(th) | Qg | Rds(on) | Qgd | Ciss | Id | tr | Comments | |||||

| SUM110N06-3m9H | 4V | 200 nC | 3.9mohm | 45nC | 15,800 pF | 110A | 160ns | Used in Texas Instruments' DRV8301-69m kit, but no longer available. | |||||

| AUIRFN8459TR | 3V | 40nC | 4.8 mohm | 14nC | 2,250 pF | 70A | 55 ns | Replaced BSO150n03MDG with these. | |||||

| BSO150n03MDG | 1.5V | 12.6nC | 20mohm | 1.4nC | 970 pF | 9.3A | 3.8 ns | Original transistor that was experiencing "shoot-through." | |||||

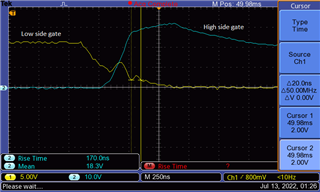

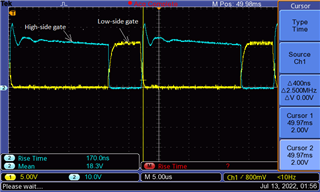

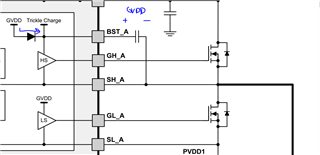

The new issue I'm seeing is illustrated by the figure below. The yellow trace is the High side gate, and the blue trace is the Low side gate of a pair (Q1 & Q2).

The high-side gate should be going up to about 34V, and it is, but all that ringing means it's only turned ON for a short period.

Any ideas what's happening here?

Thanks,

Dave