hi , chips

I have a question about drv8908-q1. Could you help me solve the question, thank you.

1.Would you please help to check why is the “OLD” happened when we add Direct Air Discharge: +/- 8KV noise to output shield line, thanks!

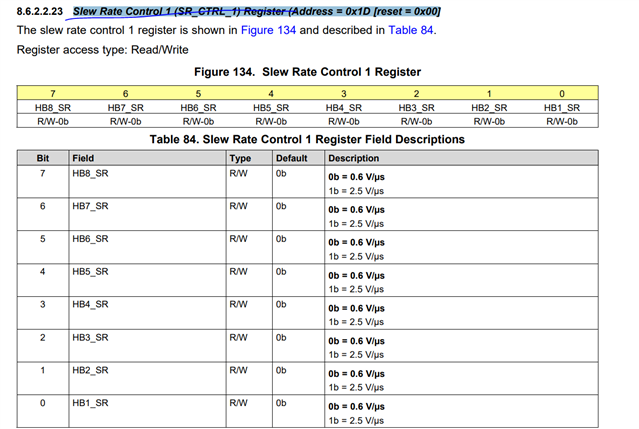

And I have check that register about OLD configration is back to default, why? and the register(address 0x07) is not back to default value,why?

2. can you tell me If there any other cases that would re-enable the open load detection (OLD) ;

3. can you tell me If there any special notification about the sets of registers when disable OLD;