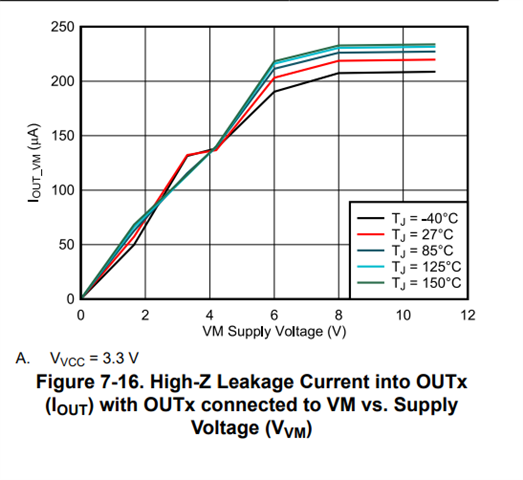

I have designed a device implementing the DRV8210DSGR and am seeing more leakage current than I would like. The datasheet states that there is some leakage in high-Z mode when connecting the outputs to VM, but it is not very clear on what to expect. My measurements show that the leakage depends completely on the OUTx-pin voltage and seem to be completely unrelated to VM. That is, placing the bridge in high-Z mode and applying a voltage to an output pin will create a leakage current roughly equal to a 20-30k pulldown resistor no matter what VM is set to. The datasheet doesn't contradict this, but is also unclear on what the leakage is.

Is this intended functionality or is there perhaps a flaw in my implementation? The implementation has a resistor divider with 100K to 3.3V and 100K to ground on one of the outputs in order to keep the output in a measurable area even when the H-bridge is disabled. Rather than sitting at 1.65V the output goes to 0.8 or so instead. It's not a huge issue in this case, but not optimal either. Can the leakage be reduced or avoided somehow?