Ive the same behavior for all register, first read aftec POR send back default value written into datasheet, second read give 0x00.

This is true when ever I read all register once, then redo reading loop, or reading a single register twice.

Changing register value, even IC_CTL to remove lock field is not working.

~~~~~~~ Info about test made ~~~~~~

Test sequence :

Set SLEEP and DRVOFF pin to wakeup the driver

Assert CS pin

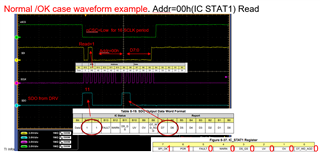

Shift address + read flag and a dummy value

Get status and register value

Result for DRV_CTRL_1

First read : Status = 0xC0 Value = 0XFF

Second read Status = 0xC0 Value = 0x00

Note:

- Reading IC_STAT_1 send back 0x40 value : POR set and SPI NOK

- When I insert a toggle of SLEEP and DRVOFF pin before second read , the second read works ( but DRV8106 had be reset in between as forcer to for to sleep mode)

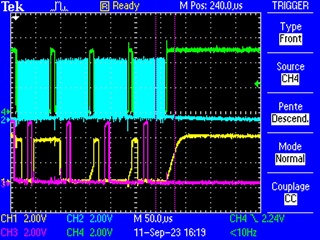

Below SPI capture ( MOSI in pink, MISO in yellow ) : 1 sucessfull read ( status 0xC0 data 0xFF), then 2 failled read 0xC0 status and 0x00 data