Hello,

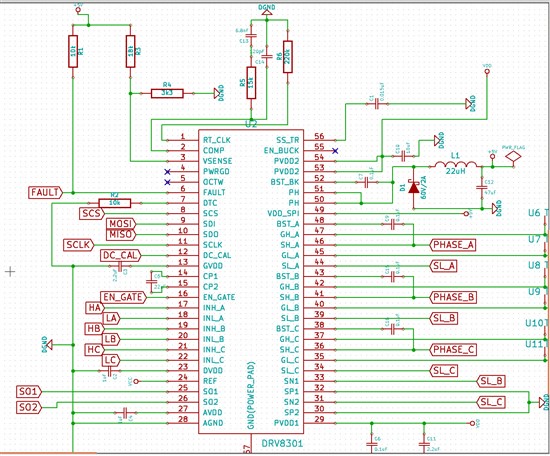

I made a custom board with the DRV8301 based on the resources and recommendations. When the board was designed, we decided to connect all the required pins so we could make the decision later in software.

Now that we've got things powered up and we think we got SPI working, there are some issues. Most of these seem related to SPI.

1. When it's all started up, we do an SPI read, which according to the docs starts with a fault condition. This indeed happens, but it also indicates a GVDD_UV condition. So the output of the first read is: 0b1000011000000000

2. The first read returns data, but other read operations always return 0. According to the data sheet, we should be able to read the contents of the control registers too, but have not been able to yet. When we use invalid frames (16-bit), the returned frames appear ok, because they indicate frame fault bits set to 1. The second status register however never returns any bit set for the device ID, even if we repeat the read multiple times. After setting the control registers and reading them back, we don't get the set values either.

3. We want to use 3-pwm mode, but this hasn't worked yet as the lower side doesn't get driven. If the lower pwm's are not left floating on the drv8301 chip, could this cause issues? The pins are not configured on the MCU.

There's another post that seems to come close to what we experience:

http://e2e.ti.com/support/applications/motor_drivers/f/38/t/365621.aspx

Here are our measurements:

- GVDD: 11 V

- DVDD: 3,3 V

- AVDD: 6,5 V

- BST_A: 10.4 V

- BST_B: 10.4 V

- BST_C: 10.4 V

The higher fets are switching.

Our SPI communication code looks like this (for each register setting we attempt), with the read command waiting for the RXNE to be set prior to taking the contents of the register.

uint16_t spi_transfer( uint16_t cmd )

{

uint16_t temp;

gpio_clear(GPIOA, GPIO15);

// start reading control register

spi_write( SPI1, cmd );

while (!(SPI_SR(SPI1) & SPI_SR_TXE));

while((SPI_SR( SPI1 ) & SPI_SR_BSY) != 0);

temp = spi_read( SPI1 );

gpio_set(GPIOA, GPIO15);

return temp;

}

So we pull SCS low, then do the write, wait for TXE to complete, do a read after RXNE is set, set SCS=1 and return the result. Is this the right way to do it, or should we not set the SCS each time? According to the data sheet, the latching occurs after either the 16-th clock cycle or the SCS bit set to 1.