Hi,

My customer is the first time to use DRV8350H,so am I. please help to review their schematic and some questions.

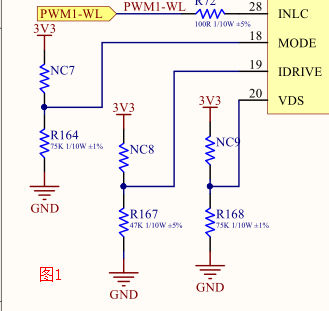

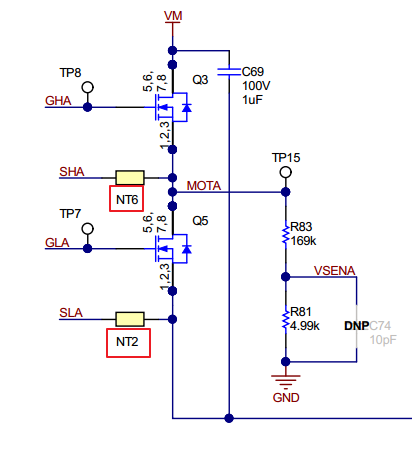

the schematic is as attached.

Q1:Please recommend the suitable component for pin 18,19 and 20 according to the used MOSFET [IPD60N10S4L-12]

BTW, it would be great if can also help to suggest suitable component for TI MOS CSD19533KCS。IPD60N10S4L-12.pdf

Q2:Without any external OCP detect circuit, please confirm is it enough and safe to just use the internal overcurrent and Short Circuit.