Hi, I recently purchased a DRV 8323RS Booster Board to run an FOC algorithm (3x PWM mode) using a Tiva C MCU (80MHz system clock) and an absolute position magnetic encoder. I am testing my algorithm on a hobby brushless motor DYS D2836 (~91mili ohms phase resistance, ~11uH phase inductance, and 0.001 Wb phase flux linkage, 7 pole pairs). PWM frequency is 5kHz (up-down counting) and VM is 15V, amplifier gains are set to 40V/V and the sampling is synchronized with the PWM (i.e. interrupt when PWM counter of phase A = 0, or LS gates are ON and HS gates are OFF) and all 3 generators are center aligned. TDRIVE is set to 2000ns and TDEAD to 400ns, HS gates set to 60mA for a rise time of ~100ns and LS gates 120mA for a fall time of ~50ns. I've checked the math of my FOC loop and it works fine. Current and position sensors outputs scale appropriately.

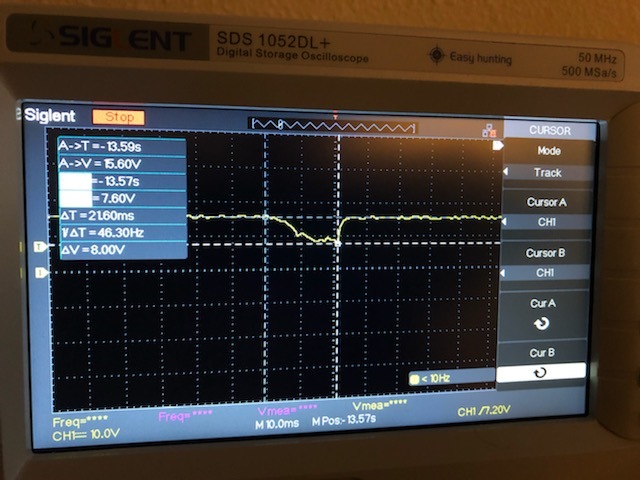

Problem: I'm using a switching power supply for my VM of 15VM. As soon as I run my algorithm I keep getting UVLO faults and my power supply dumps a lot of current (e.g. reaching the limit of my supply of ~5A). Based on the data sheet regarding Power Supplies, this failure seems to fit a low bulk capacitance problem. I think my bulk capacitance was not high enough (e.g started with a single 100uF electrolitic cap between power and ground), but the problem continued. Thus, I've added five 10uF electrolitic and five 22uF electrolitic capacitors between power and ground of my power supply to increase the capacitance, but I keep getting the same UVLO fault, the same large amount of current, and VM drops by 7V.

Questions:

1. Could this fault damage the Driver and/or mosfets?

2. How can I properly size caps for bulk capacitance?

3. Do you think the root cause is related to a different topic and not bulk capacitance?