Hi Experts,

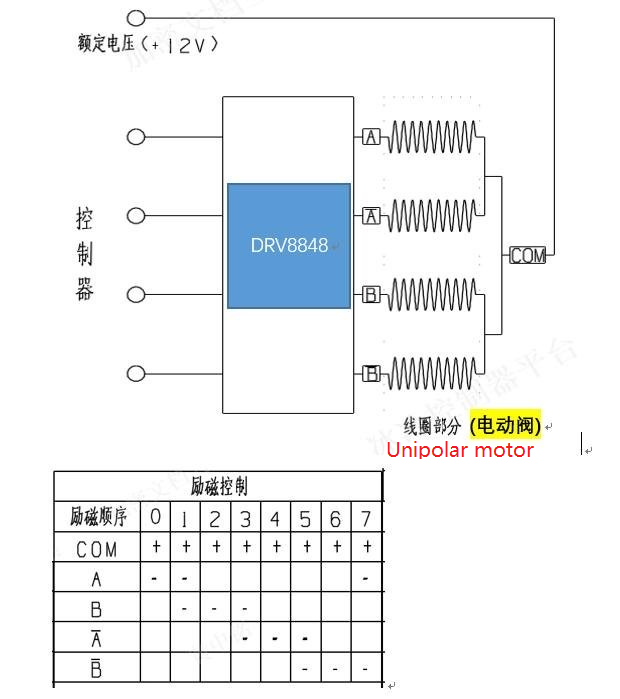

Our customer wants to use DRV8848 to drive a unipolar motor like below block diagram showing, can you help to check if we can use it?

From the datasheet description, we do not find any info regarding to such application, not sure if it will workable or not.

Thanks.