Hi Team,

The customer is experiencing below issue and needs your help.

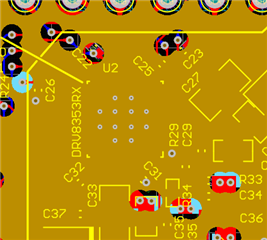

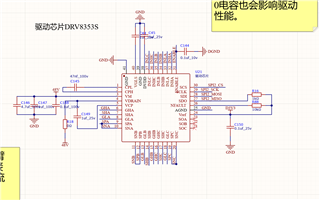

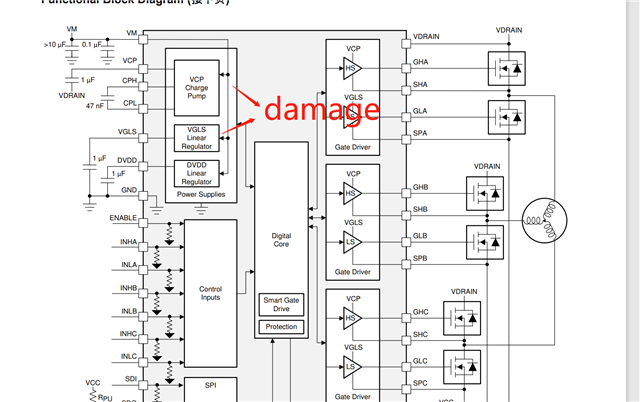

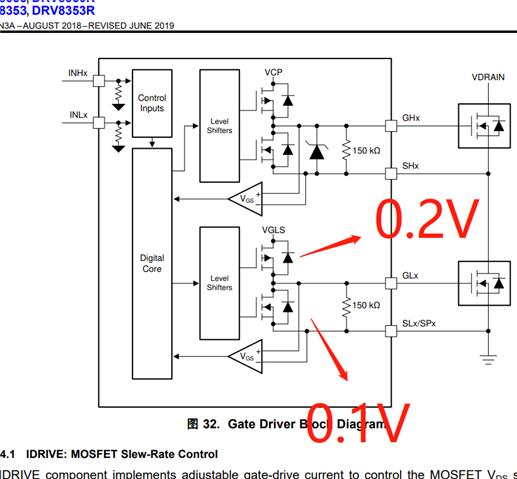

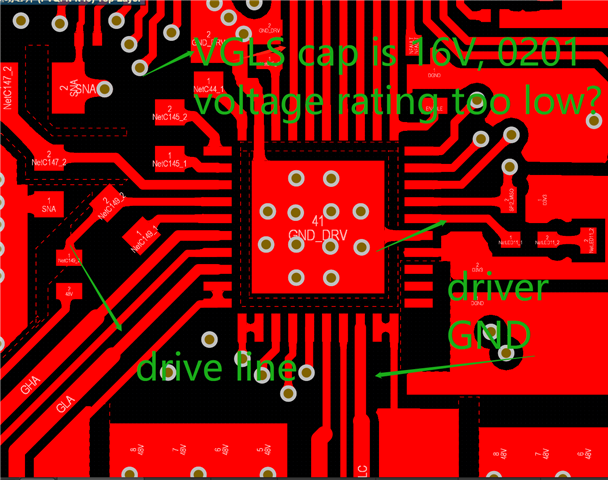

1. During the initial configuration of the chip, IDRVIEP=1A, IDRVIEN=2A. MOS is BSC040N10NS5, Qgd=12~18NC, it often happens that the totem pole circuit inside the driver chip is damaged. For example, the voltage value of the diode between VGLS and GLX is only 0.1V (normally measured near 0.59V). The voltage value between VCP and GHX is only 0.2V. After the fault occurs, the drive chip reports an undervoltage fault, and the VGLS and VCP voltages are insufficient. The customer suspected a short circuit inside the chip, and the temperature quickly rose to the alarm value after power-on.

2. After the customer reduces the drive current (IDRVIEP=0.1A, IDRVIEN=0.2A), VGLS and DVDD cannot output 11V and 5V during operation. There is a short circuit inside the chip, and the chip temperature rises sharply.

3. In the chip manual, DVDD is a 5V power supply. If it is not used, can the 1uf filter capacitor be removed?

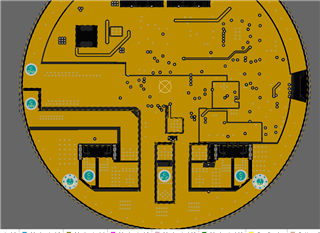

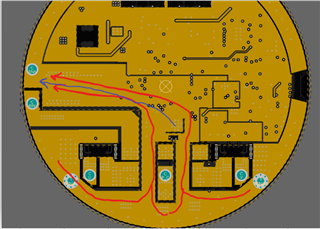

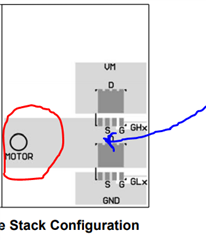

4. Whether the VDRAIN of the chip must be connected to the drain of the upper bridge arm of the MOS during PCB layout? What impact will VM and VDRAIN have in the design process? Will it cause chip damage?

Thanks.

Annie

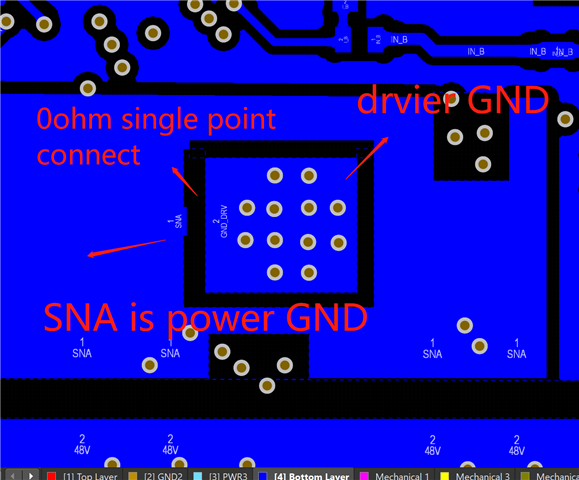

GND through a 0 ohm resistor

GND through a 0 ohm resistor