Hello.

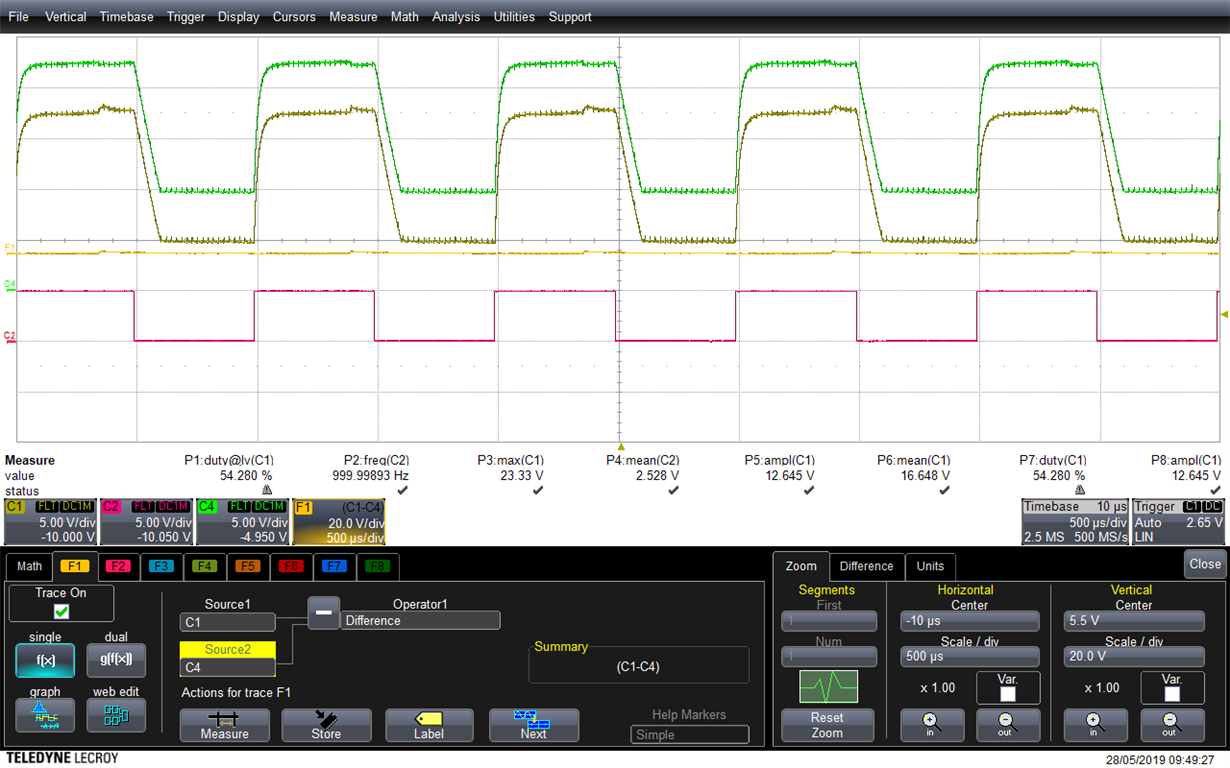

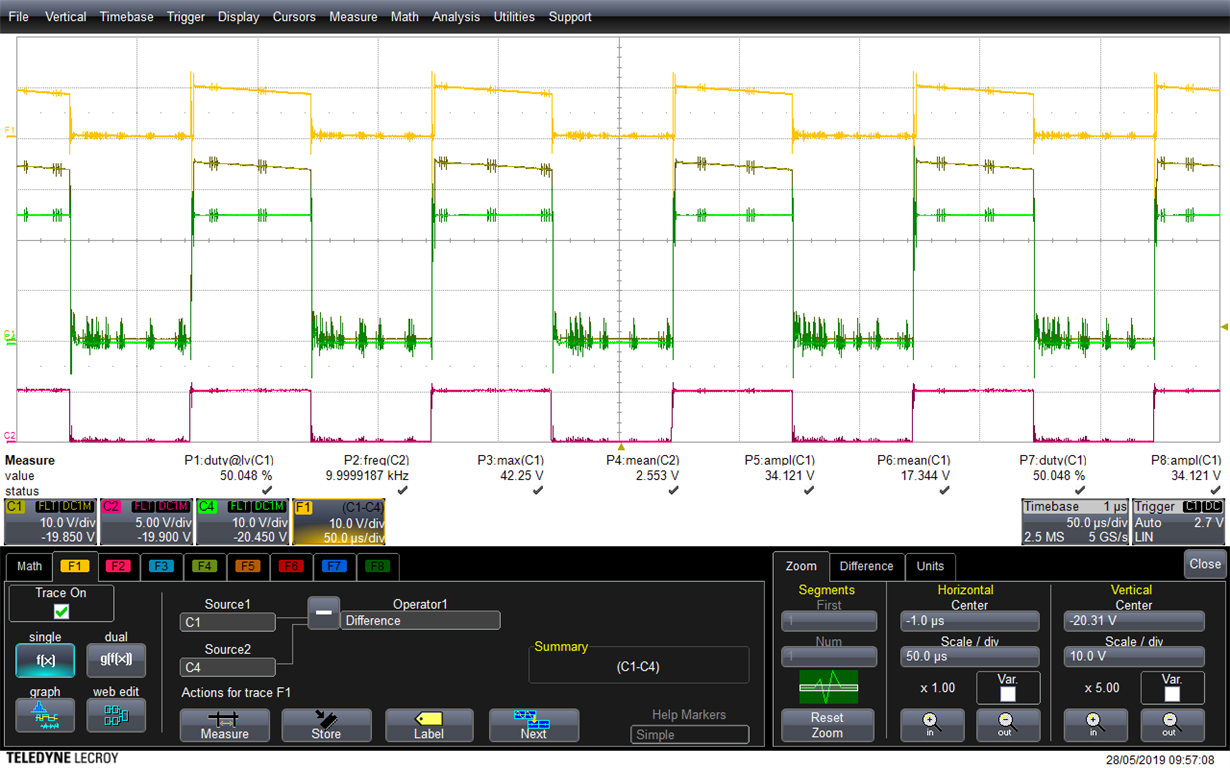

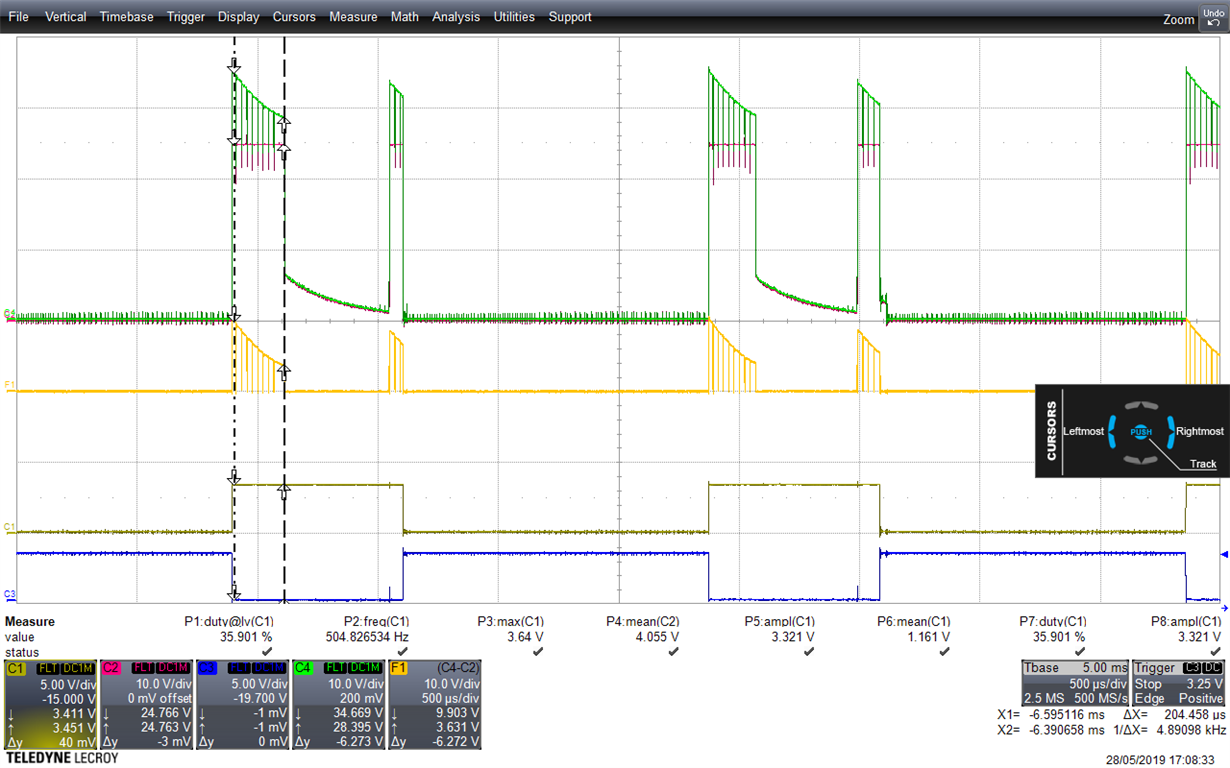

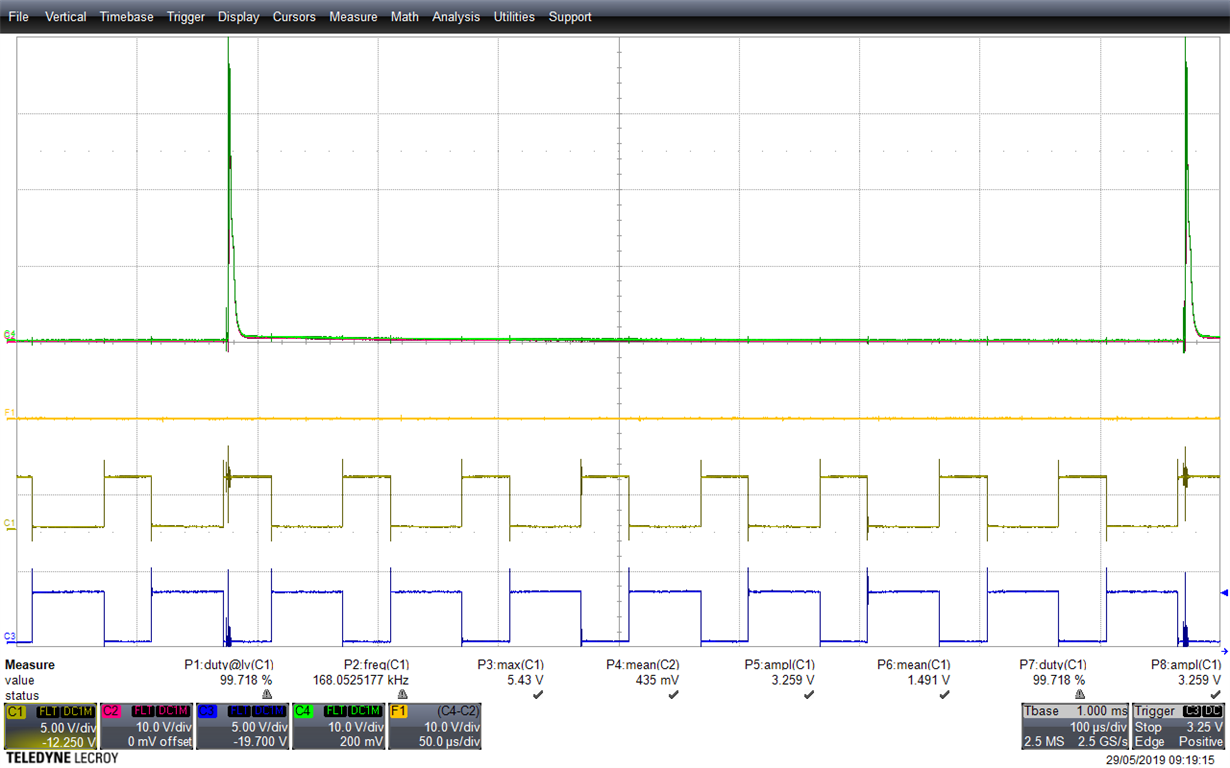

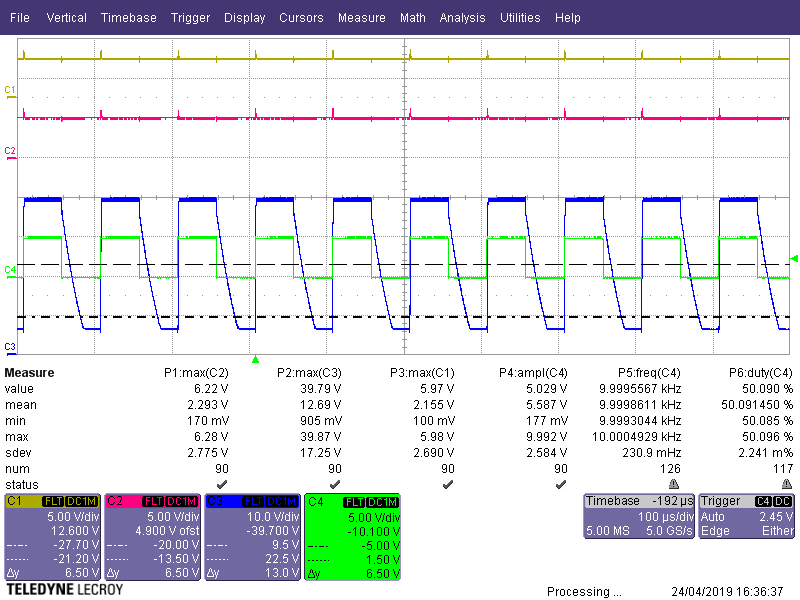

I wish to use the DRV8302 to drive a brushless motor. During my unitary test of said driver I saw that the output is not as expected when using the 6-PWM mode. On the image hereunder I have nFAULT and nOCTW on C1 and C2. C4 is my input onto INH_A which is coming from a function generator. C3 is the ouput I get on GH_A.

The signal is measured in regard to the common ground.

This problem is not observed on the low side nor when using a 3-PWM mode (high and low side).

Do you have any explanation ?

Thank you.