Hi Experts,

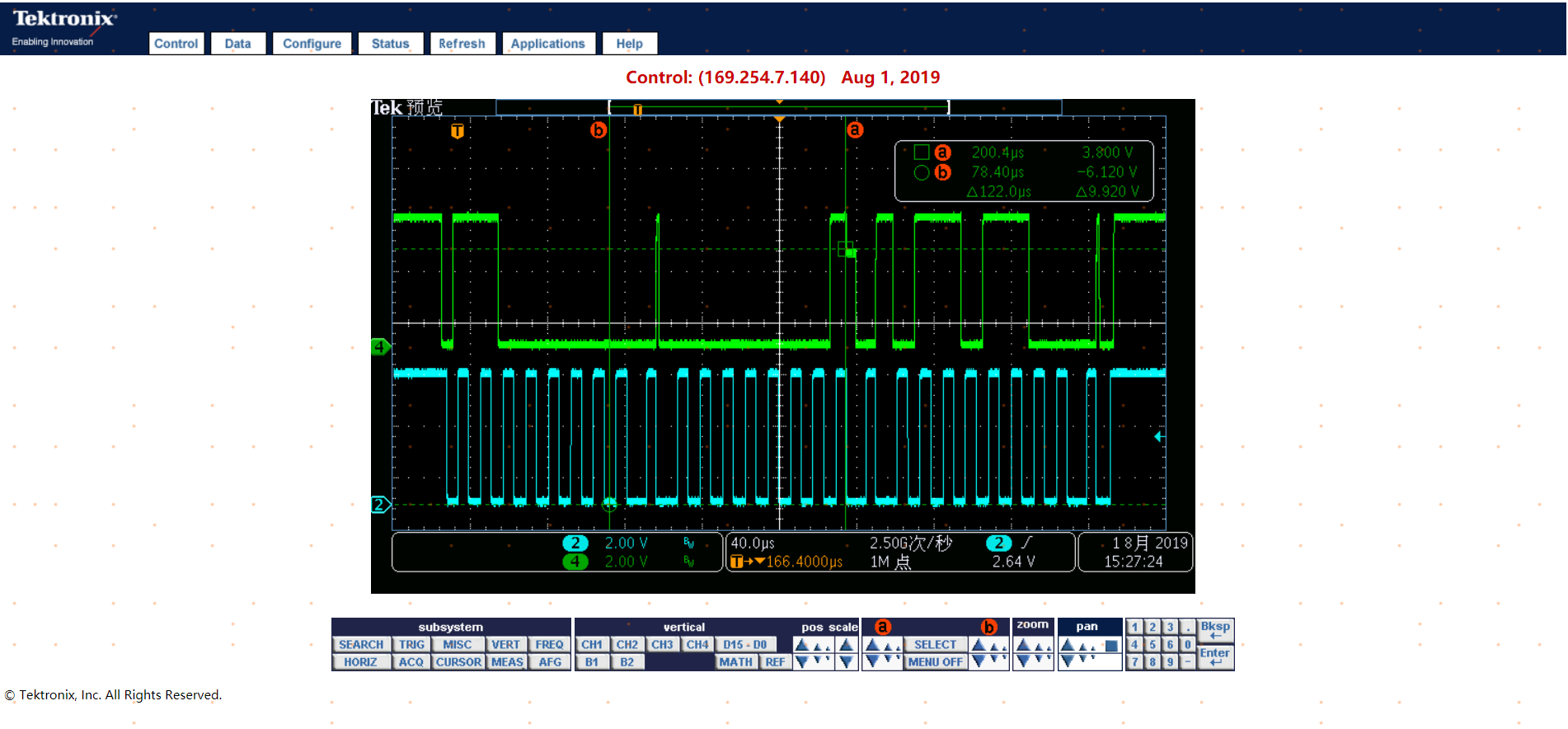

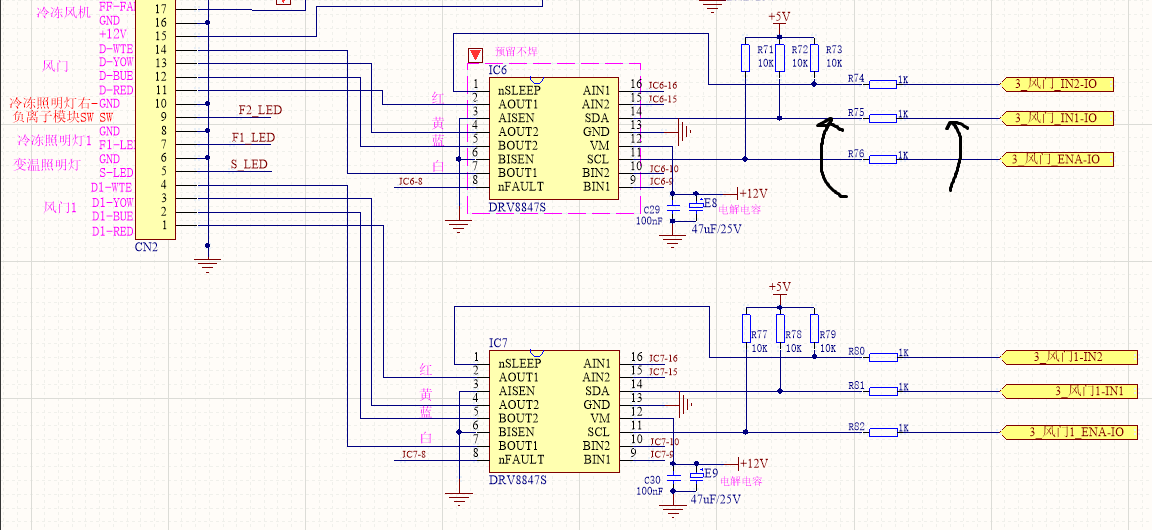

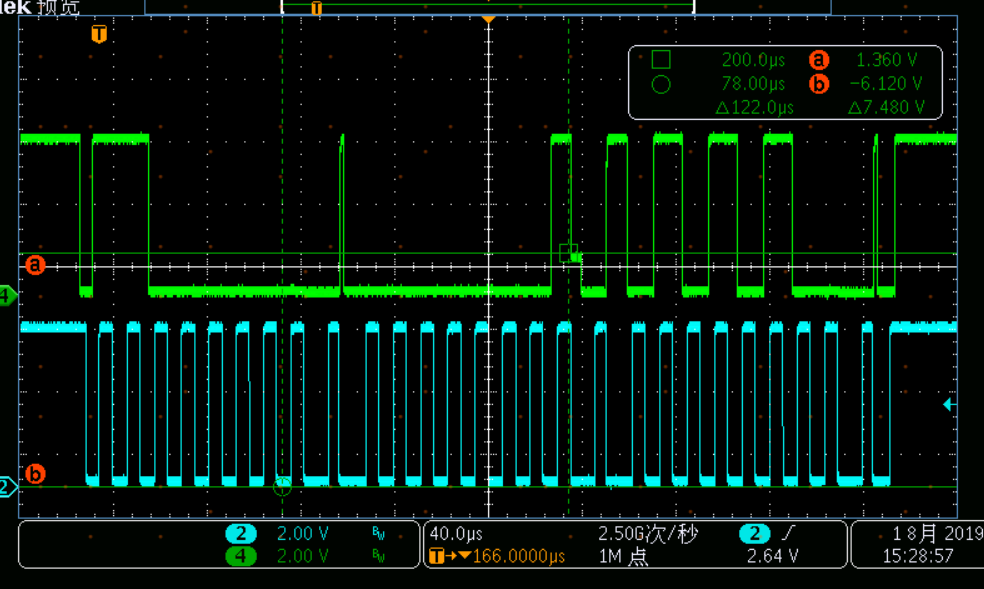

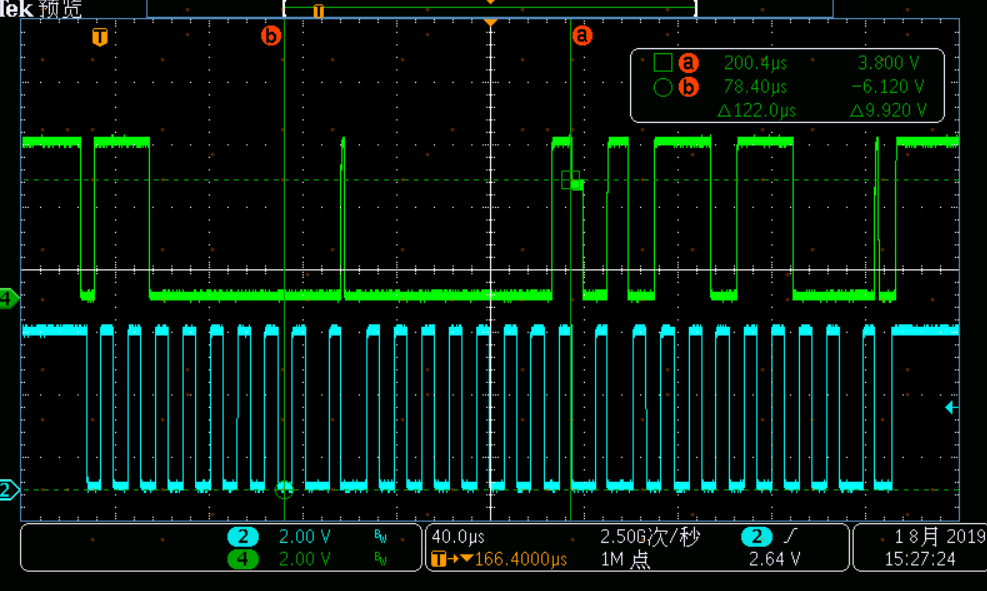

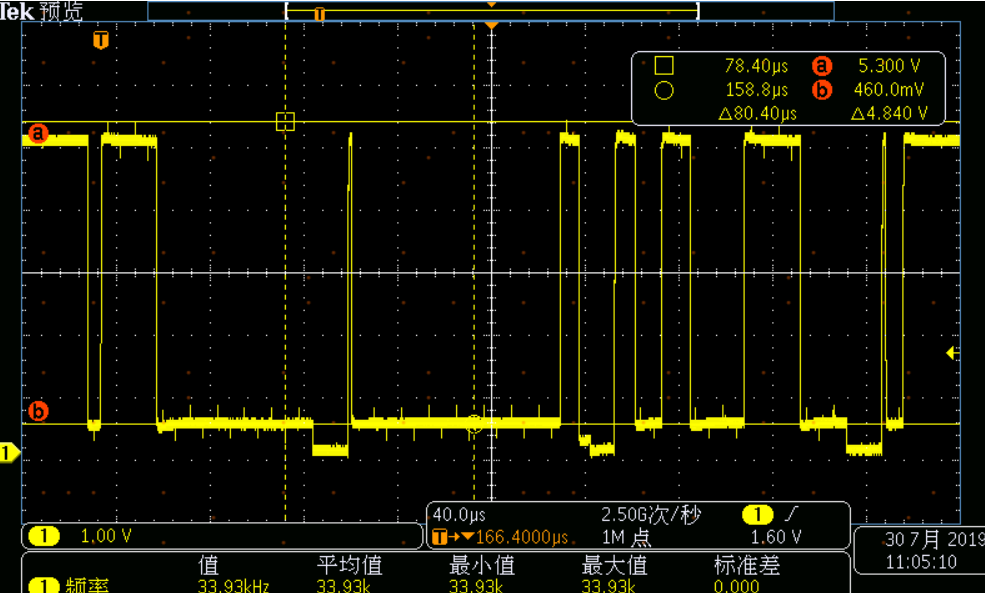

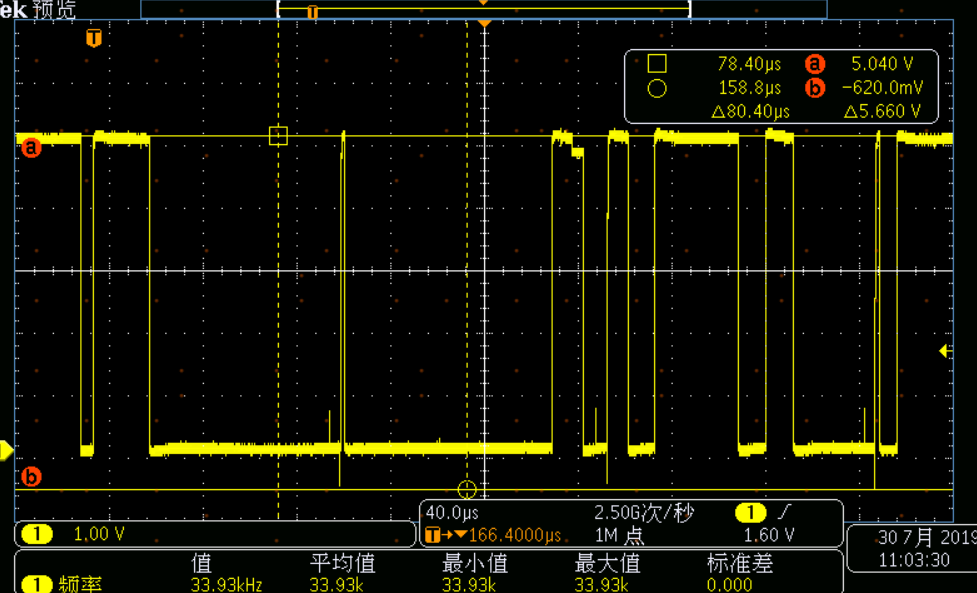

Recently our customer is debugging on our DRV8847S on their board, and captured some strange I2C SDA line waveform as below, where you will see a bar when voltage goes from high to low. Also we checked some application notes for this device, and saw one waveform looks like similar to customer's behavior, but not sure(http://www.ti.com/lit/an/slvae40/slvae40.pdf). Do you have any thoughts why there is a bar in here?

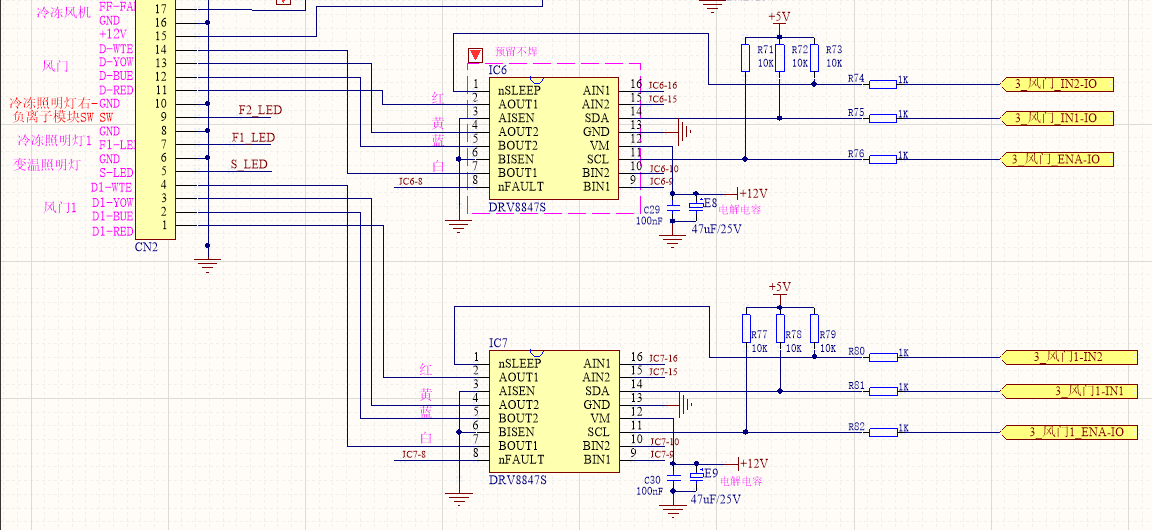

1. Strange I2C SDA line waveform captured on customer's board:

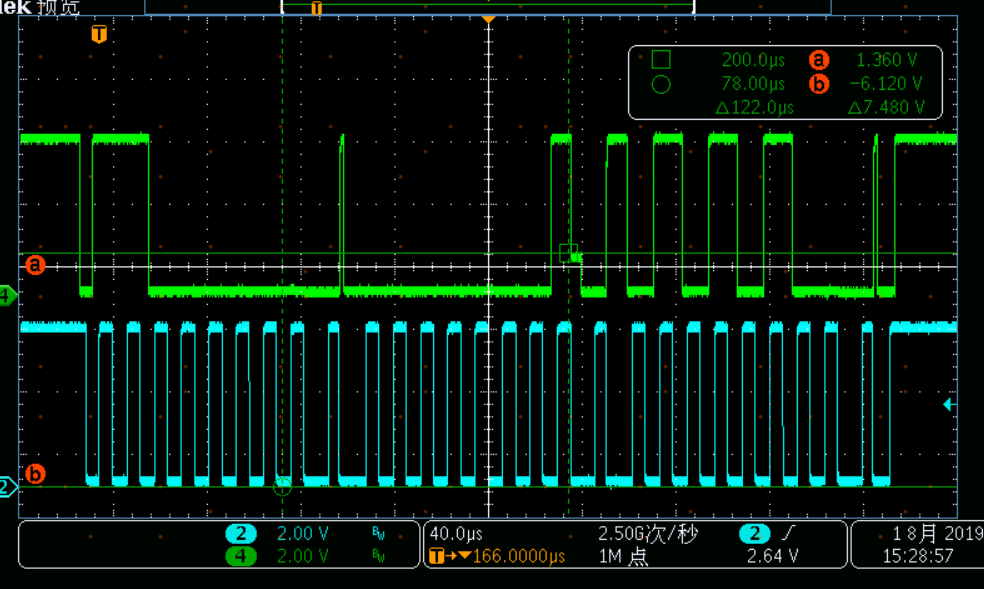

2. Looks like there is a similar behavior captured in this application note, but not sure:

Thanks a lot!